Разработка PIC-контроллера устройства измерения временных величин сигналов

Современная информационно–измирительная техника располагает совокупностью средств измерения различных физических величин электрических, магнитных, механических и др. Огромное количество из этих величин в процессе измерения преобразуется в величины электрические как наиболее удобные для передачи, усиления, сравнения, точного измерения. Поэтому в развитии современной информационно–измирительной техники преобладающее значение приобретает развитие средств измерений электрических величин.

Первые автоматические ЦИП были предложены и разработаны

Ф. Е. Темниковым в середине тридцатых годов. Первые серийноспособные цифровые приборы были разработаны и изготовлены в 1954—1956 гг. в Новосибирске и во Львовском политехническом институте под руководством М. П. Цапенко, К. Б. Карандеева и А. Я. Шрамкова.

Цифровая измерительная техника постепенно стала важнейшей отраслью измерительной техники. Номенклатура цифровых приборов непрерывно расширяется, выпускаются ЦИП различных классов точности от 0,0001 до 2% с различным числом десятичных знаков отсчета от 2 до 8 (в большинстве случаев 4—5 знаков).

Созданы автоматические цифровые приборы, основанные на новых принципах, отличающиеся дискретной, кодированной формой представления результата измерения, высокими точностью и быстродействием. Цифровые приборы решают многие новые задачи измерительной техники.

В настоящее время очень развита микропроцессорная техника и микропроцессоры имеют широкое применение. Поэтому использовать во многих случаях целесообразно микропроцессоры и заменять ими обычные логические схемы, что повышает надежность и долговечность устройства в целом за счет высокой интеграции логических элементов на кристалле полупроводника.

К микропроцессорным БИС относятся и микроконтроллеры т.к. содержат интегрированные ОЗУ, ПЗУ и подсистему ввода вывода.

1.ОСНОВНАЯ ТЕХНИЧЕСКАЯ ЧАСТЬ

1.1 Обзор аналогичных устройств

1.1.1 Классификация цифровых измерительных приборов

В каждом цифровом измерительном приборе определяется числовое значение измеряемой величины в определенной системе счисления, преобразование одного кода в другой, визуальная цифровая индикация или регистрация. Все эти операции занимают определенное время, поэтому ЦИП измеряют и выдают результат измерения дискретно во времени.

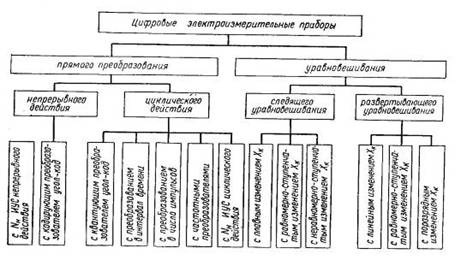

Цифровые приборы делятся на цифровые приборы прямого преобразования, уравновешивания (рисунок 1.1) и комбинированные.

Цифровые приборы прямого преобразования в зависимости от характера преобразования делятся на приборы непрерывного действия, выходной код которых следует за измеряемой величиной при каждом ее изменении, превышающем ступень квантования, и на приборы циклического действия, в которых процесс измерения циклически повторяется по заданной программе и новое значение выходного кода определяется после сброса на нуль предыдущего значения.

Рисунок 1.1

К цифровым приборам непрерывного действия прямого преобразования относятся, например, цифровые приборы с кодирующими преобразователями угол—код, в которых измеряемая электрическая величина в измерительном механизме преобразуется в угол а поворота подвижной части прибора, а угол а кодирующим преобразователем преобразуется в код.

Большинство цифровых приборов прямого преобразования являются приборами циклического действия. К ним, например, относятся цифровые приборы с вантующими преобразователями угол–код, работающими с фиксированным циклом, цифровые приборы с частотными преобразователями, с преобразователями в интервал времени.

Цифровые приборы уравновешивания построены по замкнутой схеме. В таких приборах в процессе измерения производится сравнение известной компенсирующей величины Хк и неизвестной по значению величины Х или величины, пропорциональной мгновенному значению или интегралу величины X. При этом в процессе уравновешивания одна из величин — Хк или величина, пропорциональная X, изменяется во времени.

Этот процесс уравновешивания продолжается до момента уравнивания величин Х и Хк, который обнаруживается одним измерительным устройством сравнения и усилителем некомпенсации УН.

Цифровые приборы уравновешивания подразделяются на приборы следящего уравновешивания, или следящие приборы, и приборы развертывающего уравновешивания.

1.1.2 Цифровые измерители времени

Интервал времени Тх измеряется цифровым хронометром (рисунок 1.2 а) путем сравнения с интервалом NT0. Для снижения погрешности необходимо уменьшение Т0, т. е. повышение скорости счета импульсов счетчиком. Максимальная скорость прямого счета счетчиками импульсов достигает 109 имп/сек, однако у большинства серийных счетчиков импульсов не превышает 107 имп/сек.

Снижение погрешности измерения интервала Тx возможно не только путем уменьшения T0 т. е. ступени квантования, но и путем уменьшения погрешностей d1t и d2t, возникающих при квантовании интервала времени Тх

1.1.2.1 Цифровой хронометр с генератором нониусных импульсов

Схема цифрового хронометра с генератором нониусных импульсов состоит из генератора квантующих импульсов с периодом Т0 (рисунок 1.1 б),

ключа К1 управляемого старт- и стоп-импульсами, схемы совпадения СС и ключа K2, который открывается стоп-импульсом и закрывается импульсом на выходе СС, и генератора нониусных импульсов ГНИ с периодом:

TН = T0 (1.1)

где

n — номинальный отсчет счетчика СИ2 (обычно равен 10).

Генератор ГНИ запускается стоп-импульсом, и импульсы с периодом Тн поступают на схему совпадения СС и через открытый стоп-импульсом ключ К2 на СИ2. На второй вход схемы совпадения непрерывно поступают импульсы Т0. В момент совпадения импульсов Т0 и Тн срабатывает СС и закрывает рлюч К2,поступление импульсов Тн на СИ2 прекращается.

Уравнение связи между d2t и числом импульсов N2, поступивших на счетчик СИ2, находим из равенства:

N2Tн = (T0 - d2t) + T0(N2 - 1) (1.2)

После подстановки находим:

d2t = N2T0/n (1.3)

Тогда измеряемый интервал Тх определяется по сумме отсчетов обоих счетчиков импульсов:

Tx = N1T0 + d2t = N1T0 + N2T0/n (1.4)

Следовательно, если d1t = 0, то погрешность от дискретности уменьшается в n раз.

Известны хронометры с нониусным генератором импульсов с погрешностью измерения, равной 10-9 сек.

1.1.2.2 Цифровой хронометр с линией задержки импульсов

Схема этого прибора (рисунок 1.2 в) состоит из генератора квантующих импульсов ГКИ, счетчика импульсов СИ, цифрового отсчетнрго устройства ЦОУ, преобразователя кода ПКК, линии задержки Л3 с N2н выходами и N2н схем совпадения СС. Каждый квантующий импульс Т0 поступает на ЛЗ, и через интервалы Т0/ N2н на соответствующих выходах ЛЗ появляются выходные импульсы. К каждому из N2н выходов ЛЗ подключена схема совпадения. На вторые входы всех СС поступает стоп-импульс. До прихода стоп-импульса все СС закрыты, в момент прихода стоп-импульса открывается та схема СС, на которой совпадают во времени импульс с периодом повторения Т0/ N2н и стоп-импульс, тогда:

d2t = N2T0/ N2н (1.5)

где

N2н — номер выходного канала линии задержки, к которому подключена сработавшая схема совпадения.

В преобразователе кода входной импульс от этой схемы совпадения по каналу N2 преобразуется в код управления младшей декадой цифрового отсчетного устройства.

Измеряемый интервал Тх равен:

Тх = N1T0 + d2t = N1T0 + N2T0/ N2н (1.6)

где

N2н — число секций линий задержки (обычно равно 10);

N2 — отсчет младшей декады ЦОУ;

N1 — отсчет остальных декад ЦОУ.

Известны схемы цифровых хронометров, в которых для измерения d1t и d2t последние преобразуются в амплитуды импульсов напряжения, числовое значение которых определяется амплитудным анализатором.

1.2 Разработка структурной схемы устройства

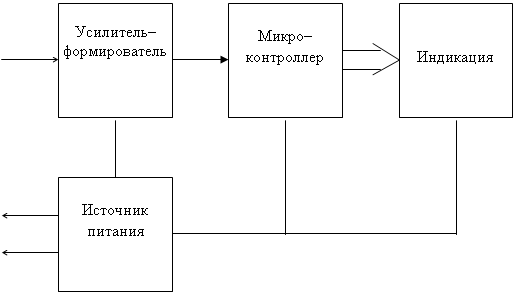

Ссылаясь на рассмотренные методы и структуры аналогичных устройств, можно сказать, что основой прибора должен быть микроконтроллер, как ядро, где происходит обработка входной информации, а также индикация, на которой отображается информация в удобном для оператора виде.

Так как устройство стационарное, работающее в лабораторных условиях, то есть необходимость разработать источник питания.

Для достаточной чувствительности устройства необходимо применить усилитель–формирователь. Тогда устройство имеет вид (рисунок 1.3).

рисунок 1.3

Принцип работы структуры заключается в следующем. На вход устройства поступает сигнал с внешнего источника. Благодаря усилителю–формирователю происходит усиление сигнала и преобразование в удобную для счета форму. Преобразованный сигнал поступает в PIC через порт и благодаря ПО происходит обработка входного сигнала в виде временной величины, что в свою очередь выводится через порт на индикацию.

1.3 Описание базового микроконтроллера

1.3.1 Регистры

Память данных разбита на два банка, которые содержат регистры общего назначения РОН и регистры специального назначения РСН. Выбор банка определяется состоянием бита RРО в регистре STATUS. Когда RPO установлен в "1", выбран банк 1, иначе — 0. Первые 12 байт каждого банка отведены под РСН. Некоторые РСН отображаются одновременно на оба банка. РОН доступны из любого банка.

Регистры общего назначения могут быть адресованы прямо или косвенно с использованием регистра косвенной адресации FSR. Регистры специального назначения используются для управления ЦПУ и функциями ввода-вывода и представленны в таблице 1.1.

Регистр STATUS содержит флаги АЛУ, параметры сброса (RESET) и биты выбора банка памяти данных. Регистр STATUS так же, как и любой другой регистр, может быть операндом для любой команды. Если регистр STATUS используется в качестве операнда для команды, которая воздействует на биты Z, DC или С, то непосредственная запись в эти биты запрещена. Более того, запись в биты -ТО и -PD запрещена. Поэтому результат команды, использующей STATUS в качестве регистра назначения, может отличаться от ожидаемого.

Регистр OPTION доступен для чтения и записи и содержит различные управляющие биты для конфигурации предделителя TMRO/WDT, самого TMR0 и подтягивающих резисторов GPIO.

Регистр INTCON доступен для чтения и записи и содержит биты разрешения прерываний: общего, периферийных устройств и TMR0, а также флаг переполнения TMR0.

Таблица 1.1 — Регистры специального назначения

| Обозначение | Описание | |||||||

| Бит7 | Бит6 | Бит5 | Бит4 | Бит3 | Бит2 | Бит1 | Бит0 | |

| Банк 0 | ||||||||

| INDF | При обращении производится доступ к ОЗУ по адресу в FSR | |||||||

| TMR0 | Регистр TMR0 | |||||||

| PCL | Младший байт счетчика команд PC | |||||||

| STATUS | IRP | RP1 | RP0 | -TO | -PD | Z | DC | C |

| FSR | Индексный регистр косвенной адресации | |||||||

| PORTA | — | — | — | RA4/T0CKI | RA3 | RA2 | RA1 | RA0 |

| PORTB | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | RB0/INT |

| EEDATA | Регистр данных Flash–ПЗУ | |||||||

| EEADR | Регистр адреса Flash–ПЗУ | |||||||

| PCLATH | — | — | — | Буфер для записи старших 5 бит РС | ||||

| INTCON | GIE | EEIE | T0IE | INTE | RBIE | T0IF | INTF | RBIF |

| Банк 1 | ||||||||

| INDF | При обращении производится доступ к ОЗУ по адресу в FSR | |||||||

| OPTION | GPPU | INTEDG | T0CS | T0SE | PSA | PS2 | PS1 | PS0 |

| PCL | Младший байт счетчика команд PC | |||||||

| STATUS | IRP | RP1 | RP0 | -TO | -PD | Z | DC | C |

| FSR | Индексный регистр косвенной адресации | |||||||

| TRISA | — | — | — | Регистр направления данных PORTA | ||||

| TRISB | Регистр направления данных PORTB | |||||||

| EECON1 | — | — | — | EEIF | WRERR | WREN | WR | RD |

| EECON2 | Регистр 2 управления Flash–ПЗУ (физически не реализован) | |||||||

| PCLATH | — | — | — | Буфер для записи старших 5 бит РС | ||||

| INTCON | GIE | EEIE | T0IE | INTE | RBIE | T0IF | INTF | RBIF |

Таблица 1.2 — Состояние регистров после сброса POR

Регистр | Состояние |

| W | xxxx xxxx |

| INDF | ---- ---- |

| TMR0 | xxxx xxxx |

| PCL | 0000 0000 |

| STATUS | 0001 1xxx |

| FSR | xxxx xxxx |

| PORTA | ---x xxxx |

| PORTB | xxxx xxxx |

| EEDATA | xxxx xxxx |

| EEADR | xxxx xxxx |

| PCLATH | ---0 0000 |

| INTCON | 0000 000x |

| OPTION | 1111 1111 |

| TRISA | ---1 1111 |

| TRISB | 1111 1111 |

| EECON1 | ---0 x000 |

| EECON2 | ---- ---- |

Регистр INDF не является физическим регистром. При обращении к регистру INDF на самом деле происходит косвенная адресация памяти данных.

Косвенная адресация реализована через регистр INDF. Любая команда, использующая регистр INDF, фактически обращается к данным, на которые указывает регистр адреса в файле (FSR). Чтение самого INDF с помощью косвенной адресации дает в результате 00h. Результатом косвенной записи в регистр INDF будет NOP.

1.3.2 Стек

PIC16F84 имеет аппаратный стек глубиной 8 13-битных слов. Стек не является частью памяти программ или данных, а указатель стека не может быть явно прочитан или модифицирован. При выполнении команды CALL или возникновении прерывания PC сохраняется в стеке. При выполнении команд RETURN, RETLW или RETFIE значение PC восстанавливается из стека. Содержимое PCLATH при этом не изменяется.

Стек работает как циклический буфер. Это означает, что после того, как в стек было помещено восемь записей, девятая помещается на место первой, десятая - на место второй, и т.д.

1.3.3 Порты ввода/вывода

PIC16F84 имеет два порта, а именно PORTA, PORTB. Некоторые каналы портов совмещают функции выводов других периферийных устройств.

PORTA — это 5-разрядный порт. RA4 имеет триггер Шмитта на входе и открытый сток на выходе. Остальные каналы порта имеют входные уровни ТТЛ и выходные буферы КМОП. Порт имеет регистр направления TRISA, с помощью которого каналы порта могут быть индивидуально настроены на ввод или на вывод.

Установка в "1" бита регистра TRISA определяет соответствующий канал PORTA как вход, т.е. выходные буферы переводятся в третье состояние. Установка в "0" бита регистра TRISA определяет соответствующий канал PORTA как выход, т.е. содержимое защелки порта выводится на соответствующий вывод микросхемы.

Чтение регистра PORTA возвращает состояние на выводах порта, тогда как запись производится в защелку PORTA. Все операции записи в порт производятся как чтение-модификация-запись, т.е. сначала производится чтение состояния выводов, затем модификация и запись в защелку. Канал RA4 также работает как вход тактового сигнала TMR0.

PORTВ — это 8-разрядный порт, который имеет регистр направления TRISB, с помощью которого каналы порта могут быть индивидуально настроены на ввод или на вывод.

Установление в "1" бита регистра TRISB определяет соответствующий какал PORTB как вход, т.е. выходные буферы переводятся в третье состояние. Установление а "0" бита регистра TRISB определяет соответствующий канал PORTB как выход, т.е. содержимое защелки порта выводится на соответствующий вывод микросхемы.

Все контакты PORTВ имеют встроенные подтягивающие резисторы. Их включением управляет один бит -RCPU, он должен быть установлен в "0". Подтягивающие резисторы автоматически выключаются, когда каналы порта настраиваются на вывод и после POR.

Все операции вывода в порт осуществляются как чтение-модификация-запись. Команды BCF и BSF, например, считывают значение порта в ЦПУ, выполняют операцию с битом и записывают результат обратно. Требуется осторожность при применении этих команд к порту, содержащему как входы, так и выходы. Например, операция BSF надбитом 5 PORTB считывает все восемь битов PORTB в ЦПУ выполняется и записывает результат в выходные защелки. Если другой канал PORTВ используется как двунаправленный и настроен в данный момент на ввод, то входной сигнал будет считан с вывода в ЦПУ и записан а защелку данных этого канала поверх предыдущего значения.

1.3.4 Таймер

Возможности TMR0:

- 8-разрядный таймер доступен для чтения и записи,

- 8-разрядный программируемый предделитель,

- выбор источника тактового сигнала (внутренний или внешний),

- выбор активного фронта внешнего тактового сигнала,

- прерывание по переполнению таймера.

Режим работы от внутреннего тактового сигнала выбирается установлением в "0" бита Т0CS. Приращение значения TMR0 производится в каждом машинном цикле (без предделителя). После записи в TMR0 нового значения инкремент счетчика запрещен два последующих цикла.

Режим работы от внешнего тактового сигнала выбирается установлением в "1" бита T0СS. Приращение значения TMR0 производится по нарастанию или по спаду, а зависимости от состояния бита T0SЕ, сигнала со входа T0CKI.

TMR0 имеет программируемый предделитель. Предделитель может быть подключен либо к TMRO, либо к WDT. Бит PSA управляет подключением предделителя.

Прерывание от TMR0 возникает при переполнении TMR0, при этом флаг T0IF устанавливается в "1" и TMR0 продолжает работу. Запретить это прерывание можно установкой в "0" бита T0IE. Процедура обработки прерывания должна установить флаг T0IF в "0" перед тем, как вновь разрешить прерывание. Прерывание от TMRO не может вывести процессор из режима SLEEP, поскольку таймер в этом режиме выключен.

1.3.5 Предделитель

8-разрядный счетчик может использоваться как предделитель для TMR0 или как постделитель для WDT. Имеется только один преддепитель, который может быть использован либо для TMR0, либо для WDT. Подключение предделителя к TMR0 означает, что WDT не может его использовать, и наоборот.

Биты PSA и PS2-PS0 определяют подключение предделителя и коэффициент деления. Когда предделитель подключен к TMR0, любая команда записи в TMR0 будет очищать предделитель. Когда предделитель подключен к WDT, команда CLRWDT очистит предделитель вместе с WDT. Предделитеяь недоступен для чтения или записи. При сбросе предделитель также очищается.

Управление подключением предделителя полностью программное, т.е. можно его переключить во время выполнения программы.

1.4 Разработка программного обеспечения

1.4.1 Обзор команд

Каждая команда PIC16F84 - это 14-битовое слово, которое разделено по смыслу на следующие части:

1. Код операции,

2. Поле для одного и более операндов, которые могут участвовать или нет в этой команде.

Система команд PIC16F84 включает в себя байт-ориентированные команды, бит-ориентированные, операции с константами и команды передачи управления. В таблицах 1.3, 1.4 и 1.5 представлены команды микроконтроллера PIC16F84.

Для байт-ориентированных команд "f" обозначает собой регистр, с которым производится действие; "d" - бит определяет, куда положить результат. Если

"d" = 0, то результат будет помещен в W регистр, при "d" = 1 результат будет помещен в "f", упомянутом в команде, в отличии от бит-ориентированных команд, в которых "b" обозначает номер бита, участвующего в команде, а "f" - это регистр , в котором этот бит расположен.

Для команд передачи управления и опреаций с константами, "k" обозначает восьми или одинадцатибитную константу.

Все команды выполняются в течение одного командного цикла. В двух случаях исполнение команды занимает два командных цикла:

1. Проверка условия и переход,

2. Изменение программного счетчика как результат выполнения команды.

Один командный цикл состоит из четырех периодов генератора. Таким о разом, для генератора с частотой 4 МГц время исполнения командного цикла будет 1 мкс.

Таблица 1.3 — Бит ориентированные команды

| Мнемокод | Название команды |

| BCF f,b | Сброс бита в регистре f |

| BSF f,b | Установка бита в регистре f |

| BTFSC f,b | Пропустить команду, если бит = 0 |

| BTFSS f,b | Пропустить команду, если бит = 1 |

Таблица 1.4 — Байт ориентированные команды

| Мнемокод | Название команды |

| ADDWF f,d | Сложение W с f |

| Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов Разработка блока определяющего длительность стимулирующего импульса для аппарата электроанальгезии Разработка блока управления фотоприёмником для волоконно-оптических систем передачи информации Разработка детектора высокочастотного излучения Разработка зарядного устройства

Актуально:

|