Интегральные логические элементы

Кафедра: Автоматика и Информационные Технологии

Лабораторная работа

«ИНТЕГРАЛЬНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ»

1. Цель и содержание работы

Изучение принципа работы и технических характеристик интегральных микросхем, приобретение навыков составления, минимизации и реализации на логических элементах простых логических функций.

2. Домашнее задание

1. Записать паспортные данные логических элементов ТТЛ серии 155 типа И-НЕ, И-ИЛИ-НЕ (8).

2. Рассмотреть основные понятия и теоремы алгебры логики. Познакомиться с методами минимизации логических функций (диаграммы Вейча, карты Карно) (2,5,7).

3. Произвести синтез комбинационной схемы. Данные взять из табл. 2.

3. Краткие сведения из теории полупроводниковой электроники

В цифровой схемотехнике простейшие логические операции осуществляются с помощью логических элементов (ЛЭ). Широкое распространение получили интегральные схемы (ИС) транзисторно-транзисторной логики (ТТЛ). Большинство ИС, выпускаемых промышленностью серийно, представляют собой ЛЭ, выполняющие функции НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ и т.д.

Возможность использования ЛЭ в цифровой аппаратуре оценивается параметрами, основными из которых являются: Еп – номинальное напряжение источника питания, равное +5В для ТТЛ элементов;

Рпот – потребляемая элементом мощность от Еп;

U0вх – входное напряжение «0»;

U1вх – входное напряжение «1»;

U0вых – выходное напряжение «0»;

U1вых – выходное напряжение «1»;

Uп – помехи статического напряжения;

Краз – нагрузочная способность;

Коб – коэффициент объединения по входу.

Для оценки большинства параметров ИС используют передаточную, входную и выходную характеристики ЛЭ (1,2).

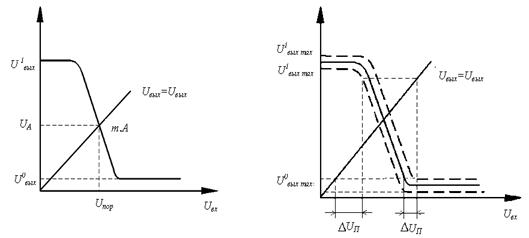

Передаточная характеристика – это зависимость выходного напряжения от входного

Uвых = F (Uвх).

Входная характеристика – это зависимость входного тока от входного напряжения Iвх = F(Uвх). Выходная характеристика – это зависимость выходного напряжения от тока нагрузки (выхода) Uвых = F(Iн). По этой характеристике находят выходные токи и напряжения при различных режимах работы логического элемента. Совместное использование входной и выходной характеристик позволяет определить нагрузочную способность, коэффициент объединения по входу, а также входное и выходное сопротивления ЛЭ. Передаточная характеристика для ЛЭ с инвертированием входных сигналов и усилением по напряжению, к числу которых относятся элементы НЕ, И-НЕ, ИЛИ-НЕ, имеет два линейных участка, соответствующих уровням логического «0» и логической «1», и узкий переходной участок (см. рис. I). Переходный участок имеет пороговую точку А, являющуюся точкой пересечения передаточной характеристики с прямой единичного усиления (Uвых = Uвх). Передаточная характеристика совокупности однотипных логических элементов из-за отклонений параметров отдельных компонентов, обусловленных нестабильностью технологических процессов изготовления интегральных микросхем, представляет собой не одну кривую, а некоторую область, ограниченную сверху и снизу двумя граничными кривыми, показанными на рис. 2.

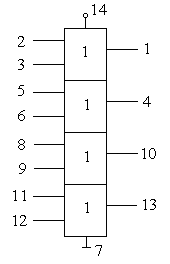

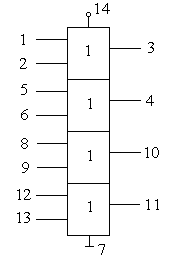

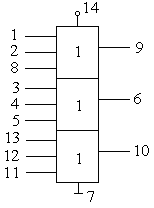

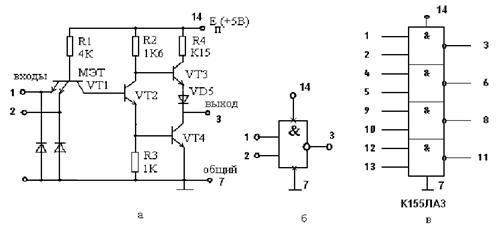

Рис. 3. Принципиальная электрическая схема элемента И-НЕ:

а – на два входа; б – условное обозначение ЛЭ; в-нумерация выводов микросхемы

По этой характеристике можно определить запасы помехоустойчивости элемента, проведя под углом 45° (при условии равенства масштабов по осям координат) касательные к нижней и верхней граничным кривым передаточной характеристики (рис. 2).

Согласно рис. 2, запас помехоустойчивости по нулевому уровню на входе (допустимый уровень положительной помехи) равен ∆U+п= Uн-Uвых макс. Запас помехоустойчивости по единичному уровню сигнала на входе или допустимый уровень отрицательной помехи на входе равен

∆U-п= U1выкмин – Uпор.

На рис. 3, а представлена принципиальная электрическая схема элемента И-НЕ, являющегося базовым элементом ТТЛ. На рис. 3, б показано условное обозначение ЛЭ на принципиальных электрических схемах. (Выводы питания +5 В и общий провод допускается не показывать). На рис. 3, в-нумерация выводов микросхемы К155ЛА3 (4 логических элемента 2И-НЕ).

Принцип работы ЛЭ И-НЕ ТТЛ

Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой.

Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ можно рассматривать как совокупность нескольких независимых транзисторов с объединенными коллекторами и базами. Такой транзистор занимает меньшую площадь, а следовательно, имеет малую паразитную емкость, благодаря чему предельное быстродействие микросхем ТТЛ выше. В зависимости от сигналов на входе, МЭТ работает в прямом (нормальном) либо в инверсном (обратном) включении. МЭТ имеет существенное различие в коэффициентах передачи тока в обоих режимах. В инверсном включении, когда напряжение на эмиттерах выше напряжения на коллекторе, коэффициент передачи тока очень мал (0,005 – 0,05).

При одновременной подаче на все входы ЛЭ сигналов с уровнем больше 2,3 В все эмиттерные р-n переходы МЭТ будут находиться в закрытом состоянии. При этом через резистор R1 и многоэмиттерный транзистор в базу транзистора VT2 поступает ток, открывающий этот транзистор. Часть тока эмиттера VT2 поступает в базу транзистора VT4, который также открывается. Транзистор VT3 при этом окажется в закрытом состоянии, т.к. напряжения, действующего на его базе, недостаточно для открытия перехода база-эмиттер транзистора VT3 и диода VD5. На выходе схемы сигнал будет иметь низкий уровень, что соответствует логическому нулю. Следует иметь в виду, что в аналогичном состоянии схема будет находиться, если все входы подсоединить к источнику электропитания (+Еп) или оставить их свободными.

Если хотя бы на один из входов подать сигнал с уровнем, меньшим 0,5 В, то транзисторы VT2 и VT4 окажутся закрытыми, т. к. ток базы МЭТ переключается через соответствующий открытый эмиттерный переход во входную цепь. Транзистор VT3 при этом будет открыт, а выходной сигнал будет соответствовать логической единице (высокий уровень). Схема будет находиться в этом же состоянии, если хотя бы один из входов соединить с общим проводом или соединить с другой схемой, имеющей сигнал логического нуля на выходе.

Следует отметить, что если вход ЛЭ никуда не подключен, т.е. «висит в воздухе», то это равноценно подключению его к высокому уровню.

Если один из входов подключен к «единице», а другой – к «нулю», то ЛЭ ТТЛ будет реагировать на низкий потенциал, т. к. он имеет приоритет перед высоким потенциалом.

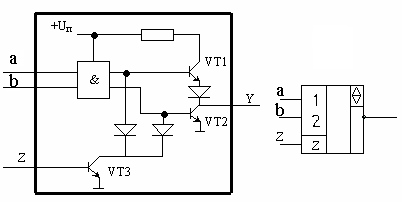

Микросхемы с тремя логическими состояниями

Устройства, оперирующие с дискретной информацией, при высоком уровне выходного напряжения имеют малое сопротивление между выводом «Выход» и шиной питания. В противоположном состоянии у «Выхода» малое сопротивление по отношению к общей шине. В обоих случаях выходной вывод имеет определенный электрический потенциал, который воздействует на входы последующих приборов (МС).

Существует категория МС, способных принимать и третье состояние, когда выход МС отключен от нагрузки. Такое состояние называют ВЫСОКОИМПЕДАНСНЫМ. Перевод МС в это состояние осуществляется по специальному входу Z. В зависимости от конкретного типа МС отключение выхода может осуществляться 1 или 0. Упрощенная электрическая схема элемента с тремя состояниями представлена на рис. 4. Когда на входе Z низкий уровень, то VT3 заперт и не влияет на работу схемы. Если Z имеет высокий уровень, то VT3 открыт и базы транзисторов VT1 и VT2 соединены с низким потенциалом (земля). Транзисторы VT1 и VT2 закрыты.

В результате связь логической части элемента с его выходом разрывается, элемент со стороны выхода приобретает высокий импеданс. Уровень потенциала на выходе неопределен (плавающий) – он может быть любым в зависимости от соотношения токов утечки VT1 и VT2. Третье состояние в отличие от 1 и 0 обозначается Z, а символ такого выхода – ромб с поперечной чертой. Элементы с 3 состояниями выхода разработаны специально для применения в качестве выходного управляемого буфера для подключения цифровых блоков к магистралям.

МС с открытым коллектором

Выходы некоторых МС выполнены так, что верхний выходной транзистор и относящиеся к нему элементы отсутствуют. Это так называемые элементы со свободным (открытым) коллектором (рис. 5).

На его выходе формируется сигнал только низкого уровня. Поэтому для нормальной работы выходного транзистора коллектор следует подключить к источнику питания через внешнюю нагрузку: резистор, элемент индикации, реле и т.п.

Для выпуска таких МС есть по меньшей мере две причины:

1. Выходной транзистор может быть использован для управления внешними устройствами, которые к тому же могут работать от других источников питания. Например, МС 155 ЛА11 позволяет под-водить к выходному транзистору до 30 В. Эти МС легко также вводить в линейный (усилительный) режим.

2. ЛЭ с открытым коллектором допускают параллельное подсоединение нескольких выходов к общей нагрузке. Такое объединение выходов называют МОНТАЖНОЙ (ПРОВОДНОЙ) ЛОГИКОЙ.

Имея дело с монтажной логикой, следует учитывать, что каждый компонент схемы утрачивает самостоятельность и действует как элемент общей системы. Так, если на одном выходе низкий потенциал, то тот же потенциал окажется на выходе всей системы. Чтобы обеспечить логическую 1 на общем выходе, необходимо иметь логические 1 на всех выходах.

Каждый из ЛЭ производит операцию И-НЕ:

![]()

![]() .

.

Следовательно:

Fвых![]() .

.

Преобразовав последнее выражение на основе закона Де Моргана, получим:

![]() ,

,

или

![]() .

.

Из этих выражений следует, что ЛЭ с объединенными выходами функционируют подобно ЛЭ И-ИЛИ-НЕ, выполняя операцию ИЛИ-НЕ по отношению к входным переменным, связанным операциями И в каждом ЛЭ. Такое толкование послужило причиной наименования «МОНТАЖНОЕ ИЛИ». Однако для положительной логики верно «монтажное И». Схема подключения микросхем с открытым коллектором к общей нагрузке представлена на рис. 6.

Выполнение логических функций на логических элементах

Сколь угодно сложные логические функции можно реализовать с помощью набора логических элементов. Наибольшее распространение получил потенциальный способ представления информации, при котором «0» и «1» соответствует низкий или высокий уровень напряжения в соответствующей точке схемы. Сигнал сохраняет постоянный уровень (нулевой или единичный) в течение периода представления информации (такта). В цифровых устройствах все данные, необходимые для вычислений, а также результаты представляются в виде набора дискретных сигналов, принимающих одно из возможных значений «0» или «1». Преобразование цифровой информации часто осуществляется в комбинационных схемах (КС). Комбинационной называется логическая цепь, состояние которой однозначно определяется набором входных сигналов и не зависит от предыдущих состояний.

Для описания комбинационных схем используется математический аппарат булевых функций – алгебра логики. Переменные Х1, Х2,…, Хn называются двоичными, если они принимают только два значения: «0» и «1». Функция от двоичных переменных Y(Х1, Х2., Хn) называется булевой, если она также принимает два значения «0» и «1». Связь между входными и выходными сигналами в КС аналитически описывается булевыми функциями. Существуют различные способы задания или представления булевых функций: словесное описание, табличный способ, алгебраический способ.

От таблиц истинности можно перейти к алгебраической форме представления функций. В такой форме удобно производить различные преобразования функций, например, с целью их минимизации.

Основные булевы функции двух переменных, их обозначение и наименования приведены в табл.I.

Система, содержащая функции конъюнкции, дизъюнкции и отрицания, является функционально полной. К ним относятся Стрелка Пирса и Штрих Шеффера.

Таблица 1

| Аргументы | Обозначения | Наименование |

| ||

| ||

| 1 1 0 0 |

| Отрицание или инверсия |

| 0 1 1 1 |

| Дизъюнкция |

| 0 0 0 1 |

| Конъюнкция |

| 0 1 1 0 |

| Сложение по модулю 2 (неравнозначность) |

| 1 0 0 0 |

| Стрелка Пирса |

| 1 1 1 0 |

| Штрих Шеффера |

| 1 0 0 1 |

| Равнозначность |

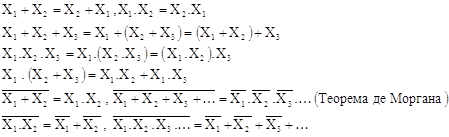

Основные теоремы алгебры логики

![]()

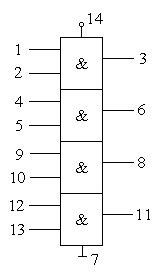

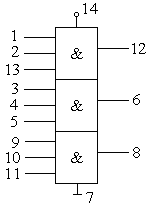

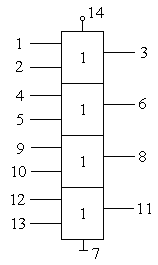

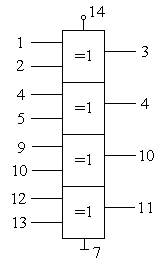

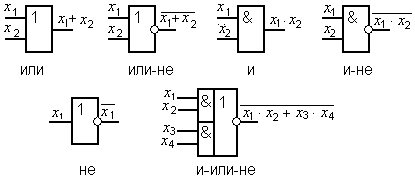

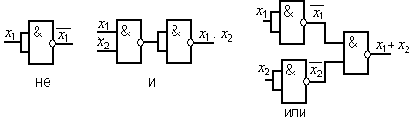

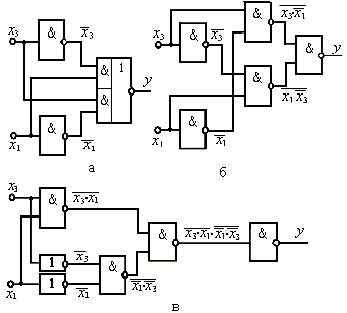

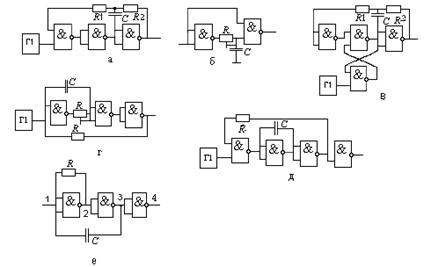

Элементарные логические операции над двоичными переменными реализуются электронными схемами – логическими элементами. Один и тот же закон преобразования информации можно рассматривать, используя различные типы комбинаций ЛЭ и связи между ними. На рис. 7 показана функционально полная система совокупности элементов И, ИЛИ, НЕ. На рис. 8 показана реализация логических операций НЕ, ИЛИ, И только с помощью одного элемента И-НЕ.

Рис. 7. Функционально полная система элементов И, ИЛИ, НЕ

Рис. 8. Реализация логических операций в базисе И-НЕ

Синтез переключательной функции

Любая логическая функция может быть представлена в дизъюнктивной или конъюнктивной нормальной форме (ДНФ или КНФ). ДНФ представляет собой логическую сумму элементарных произведений, каждое из которых аргумент или его отрицание входит не более одного раза.

Если каждое слагаемое содержит все переменные или их отрицания, то имеет стандартную форму (СДНФ): совершенную дизъюнктивную нормальную форму (СДНФ), которая является одним из вариантов алгебраического способа задания булевых функций.

Синтез переключательной функции состоит в получении ее ДНФ или КНФ и получении минимальной формы функций. При синтезе схем выполняется задача построения схем с использованием минимального числа элементов в базисе И-НЕ или ИЛИ-НЕ.

Синтез комбинационных схем с одним выходом осуществляется в следующей последовательности.

На первом этапе осуществляется запись условий функционирования в виде логической функции, словесно в виде таблиц истинности, структурных формул.

На втором этапе осуществляется запись и минимизация структурной формулы, т.е. осуществляется приведение переключательной функции к совершенной нормальной форме и ее минимизация.

На третьем этапе осуществляется запись минимизированной структурной формулы на заданном базисе. Чаще всего в универсальных базисах И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ.

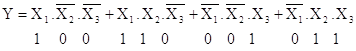

На четвертом этапе составляется структурная схема, определяющая число элементов и необходимые соединения между ними. Рассмотрим пример синтеза комбинационной схемы. Пусть заданы условия функционирования в виде таблицы истинности (табл. 2, вариант 13). Записываем структурную формулу в виде СДНФ по таблице истинности

(1)

(1)

Число слагаемых определяется числом единичных наборов (Y = 1) таблицы истинности, а число сомножителей определяется числом независимых переменных, входящих в рассматриваемые наборы.

Для реализации этой функции необходимо иметь 4 трехвходовых элемента И и один четырехвходовый элемент ИЛИ.

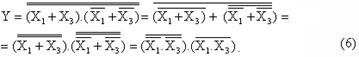

Минимизацию структурной формулы (1) произведем при помощи диаграммы Вейча (рис. 9). Получаем выражение

![]()

![]()

которое также можно получить, применив правило склеивания,

![]()

Полученную минимизированную структурную формулу можно также представить в виде

![]()

Производим преобразования структурных формул (2) и (4) в базисе И-НЕ, используя законы инверсии (формулы де Моргана):

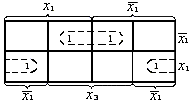

![]()

Структурные схемы, составленные по формулам (2), (5) и (6), приведены на рис. 10. Видим, что после минимизации для реализации функции требуется меньшее число логических элементов.

Рис. 9. Минимизация переключательной функции при помощи диаграмм Вейча

Рис. 10. Примеры реализации минимизированной функции согласно выражениям (2), (5), (6)

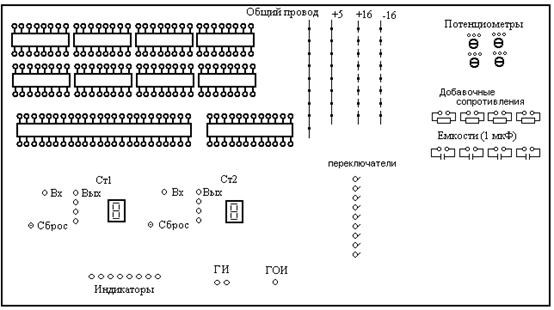

4. Используемая аппаратура

Лабораторный стенд, лицевая панель которого представлена на рисунке в прил. 1, цифровой вольтметр, приборы для измерения постоянных токов и напряжений, осциллограф типа С1–6В (или другой).

5. Подготовка к работе

Изучить параметры интегральных схем серии К155 (I).

Изучить описание лабораторной работы.

Изучить описание лабораторной установки (см. прил. 1).

Произвести синтез комбинационной схемы. Данные взять из табл. 2.

Таблица 2

X1 | X2 | X3 | Варианты Y У | ||||||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | |||

0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 1 1 1 0 1 0 1 | 1 1 0 0 1 0 1 0 | 0 0 1 0 0 1 1 1 | 0 0 0 1 1 1 0 0 | 1 1 1 0 0 0 1 1 | 1 1 0 1 0 0 0 1 | 0 0 0 1 1 1 1 0 | 1 0 0 0 1 1 1 1 | 1 0 1 0 1 1 1 0 | 0 1 0 1 1 0 0 1 | 0 0 0 1 0 1 1 1 | 0 1 0 1 0 1 0 1 | 0 1 0 1 1 0 1 0 |

По заданной таблице истинности написать логическое выражение в СДНФ. Произвести минимизацию, используя эвристические методы и карты Карно. По полученному выражению составить структурную схему.

6. Порядок выполнения работы

Познакомиться с лабораторным стендом и с наборным полем стенда. Найти ручки управления и необходимые приборы на наборном поле стенда.

– Определение статических характеристик.

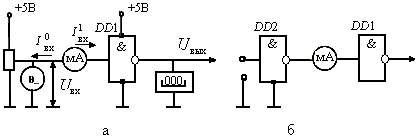

Для определения статических характеристик и параметров ИМС ТТЛ нужно собрать схему исследования согласно рис. 11, а (источник +5 В подключается к ЛЭ при включении питания стенда). Выходное напряжение измеряется цифровым вольтметром.

Изменяя напряжение на входе с помощью потенциометра В1, фиксировать входной ток, входное и выходное напряжения. Особо отметить входное напряжение, при котором Iвх = 0. Для уверенного построения характеристик следует получить 8–10 точек отсчетов, увеличивая их частоту при быстром измерении той или иной величины.

Рис. 11. Схемы для экспериментального изучения передаточной и входной характеристик

Рис. 12. Схемы для снятия выходных характеристик

Измерить входной ток I0вх и I1вх при работе ЛЭ друг на друга. Для этого собрать схему измерения согласно рис. 11 (б). Для получения на выходе DD2 низкого уровня – «0», вход ее необходимо подключить к высокому уровню – «I». Для обеспечения «I» – вход подключить к низкому уровню – «0».

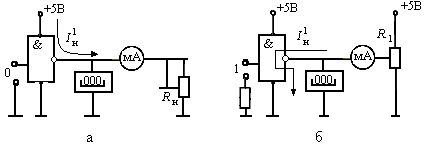

– Исследование выходных характеристик

Собрать схему измерения согласно рис. 12а, подключив вход DD1 к «0». Изменяя величину Rн, регистрировать ток I1н = I1вх и U1н = U1вх

Внимание! Следите, чтобы выходной ток не превысил допустимый для данного типа ИМС. Данные свести в табл. 3.

Изменить схему, подключив вход ЛЭ к «I». В этом случае ток нагрузки «втекает» в ЛЭ. Изменяя напряжение делителя R1, регистрировать I0н и U0вых. Данные свести в табл. 3.

Таблица 3

U0вых, В | ||||||||||

I0н, мА |

– Исследование ЛЭ с тремя состояниями выходной проводимости

Рис. 13. Схема исследования ЛЭ в третьем состоянии

Собрать схему (см. рис. 13). На вход ЛЭ DD1 подать «1». На выходе элемента окажется низкий уровень напряжения, что и будет зафиксировано вольтметром. На вход DD2 подать «0». Убедиться, что это не повлияло на состояние выхода DD1. Подключить вход DD2 к ‘1’. При этом на выходе инвертора будет низкий потенциал и он закроет транзистор VT4 микросхемы DD1. В результате оба выходных транзистора DD1 окажутся закрытыми, что соответствует третьему состоянию с высоким выходным сопротивлением.

– Помехоустойчивость ТТЛ

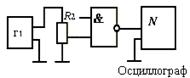

Собрать схему согласно рис. 14. Постепенно увеличивая амплитуду импульсов на входе ЛЭ, отметить момент, когда на выходе появятся заметные помехи, составляющие 0,1 от полной амплитуды выходного напряжения. Измерить осциллографом амплитуду импульсов на входе.

Рис. 14. Схема для определения помехоустойчивости ЛЭ ТТЛ

Рис. 15. Схемы формирователей и генераторов на ТТЛ элементах. Сопротивление RI может отсутствовать, сопротивление R2 выбирать в пределах к2 – 4к

– Исследование комбинационной схемы

– Проверить соответствие таблице истинности преобразований, представленных на рис. 5. Для этого подавать на вход ЛЭ уровни «О» и «I», отмечая результат на выходе.

– Собрать спроектированную комбинационную схему и убедиться в правильности ее функционирования. Входные сигналы Х и Т взять с регистра кодов. Выход контролируется с помощью лампочки индикации.

– Формирователи на ЛЭ

Собрать одну из схем формирователей на ЛЭ ТТЛ и убедиться в ее работоспособности с помощью осциллографа (рис. 15). Запускающие импульсы и перепады напряжения взять с соответствующих выходов, расположенных на наборном поле.

Подать на один вход схемы И-НЕ импульс с ГИ, а на другой – импульс со спроектированного формирователя (оба импульса должны быть положительной полярности). Сравнить длительность импульса на выходе ЛЭ с длительностями на входе. Изобразить осциллограммы, объяснить результат.

7. Обработка результатов измерений

7.1 По результатам измерений построить графики передаточной Uвых = F(Uвх), входной Iвх = F(Uвх) и выходной Uвых = F(Iвых) характеристик. Из графиков определить пороговое напряжение, входное сопротивление для низкого и высокого уровня напряжения на входе (0,4 и 2,4 В), а также выходное сопротивление при низком и высоком уровнях напряжения на выходе:

Rвых = ∆ Uвых / ∆Iн(Uвх).

По полученным результатам вычислить коэффициент объединения по входу и нагрузочную способность рассмотренного ЛЭ.

7.2 Записать логическую функцию выбранного варианта. Показать этапы ее минимизации. Составить схему соединений ЛЭ полученной функции в базисе И-НЕ (И-ИЛИ-НЕ).

Объяснить полученные результаты.

8. Содержание отчета

В отчете к лабораторной работе представить:

– схемы измерений, таблицы результатов и расчеты,

– этапы анализа логической функции и ее минимизации, схемы соединений;

– схемы для проверки таблиц истинности и результаты;

– схему формирователя с анализом ее работы;

– осциллограммы работы формирователя.

Библиографический список

1. Угрюмов Е.П. Цифровая схемотехника: учебное пособие для вузов / Е.П. Угрюмов. 2-е изд., перераб. и доп. СПб.: БХВ – Санкт-Петербург, 2004.

800 с.: ил.

2 Бабич Н.П. Компьютерная схемотехника./ Н.П. Бабич, И.А. Жуков. Киев.: «МК-Пресс», 2004. 576 с.: ил.

3 Алексенко А.Г. Основы микросхемотехники/ А.Г. Алексенко. 3‑е изд., перераб и доп. М.: ЮНИМЕДИАСТАЙЛ, 2002. 448 с.: ил.

4 Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования/ Ю.В. Новиков. М.: Мир, 2001. 379 с.: ил.

5 Прянишников В.А. Электроника: курс лекций / В.А. Прянишников. СПб.: «Корона принт», 1998. 400 с. ил.

6 Завадский В.А. Компьютерная электроника / В.А. Завадский. Киев: ТОО ВЕК, 1996. 368 с. ил.

7 Опадчий Ю.Ф. Аналоговая и цифровая электроника / Ю.Ф. Опадчий, О.П Глудкин, А.И Гуров. М.: Изд. «Горячая линия – телеком», 1999. 768 с. ил.

8 Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре/ Е.А. Зельдин. Л.: Энергоатомиздат, 1986. 280 с. ил.

9 Шило В.Л. Популярные цифровые микросхемы: справочник/ В.Л. Шило. 2-е изд. Челябинск: Металлургия, Челябинское отд-ние, 1989. 352 с. ил.

Приложение 1

Описание лабораторной установки

Измерение параметров интегральных логическихсхем осуществляется на универсальном лабораторном стенде.

Универсальный лабораторный стенд имеет на передней панели ряд стабилизированных источников питания. Источники питания с помощью внешних проводничков подключаются к исследуемым схемам. С помощью таких же проводничков соединяются соответствующие выводы микросхем. Измерительные приборы подключаются к схеме внешними проводами.

На рисунке представлено коммутационное поле лицевой панели лабораторного стенда. На ней имеются выводы разъемов, в которые можно устанавливать исследуемые микросхемы. На стенде имеются генераторы одиночных импульсов (ГОИ) и непрерывной последовательности импульсов (ГИ), лампочки индикации состояния ЛЭ, счетчики импульсов (СТ1 и СТ2) с цифровым индикатором, переключатели и некоторые другие элементы, необходимые для выполнения исследований.

Приложение 2

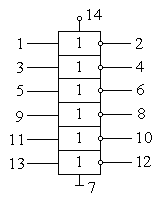

| Шесть элементов НЕ | Шесть буферных формирователей с открытым коллекторным выходом | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛН1, К155ЛН2, К155ЛН3, К155ЛН5, КP1533ЛН1, КP1533ЛН2 |

К155ЛН4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

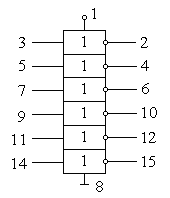

| Шесть логических элементов с буферным выходом | ||||||||||||||||||||||||||||||||||||

К564ЛН2 | ||||||||||||||||||||||||||||||||||||

|

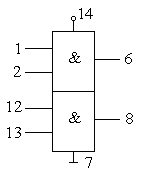

| Два логических элемента 2И | Два логических элемента 4И | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛИ5 |

К555ЛИ, КР1533ЛИ6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

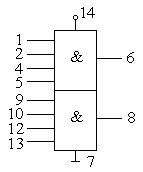

| Четыре логических элемента 2И | Три логических элемента 3И | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛИ5 |

К555ЛИ1, КР1533ЛИ6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Четыре логических элемента 2ИЛИ | Четыре логических элемента исключающее ИЛИ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛЛ1, К555ЛЛ1, КР1533ЛЛ1 |

К564ЛП2, К176ЛП2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Четыре логических элемента 2ИЛИ-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛЕ1, К555ЛЕ1, К155ЛЕ5, К155ЛЕ6 |

К561ЛЕ5, К564ЛЕ5 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Три логических элемента 3ИЛИ-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛЕ4, К555ЛЕ4 |

К561ЛЕ10, К564ЛЕ10 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||