Разработка электрической структурной, функциональной, принципиальной схем учебного комплекса по интерфейсам ввода-вывода

микросхема учебный комплекс интерфейс

Интенсивное развитие микропроцессорной техники обуславливает расширение области применения средств автоматизации управления. В настоящее время микропроцессоры и микроЭВМ широко применяют в качестве основных элементов цифровых вычислительных устройств различного назначения, в частности устройств обработки информации.

Поступательное развитие микроэлектроники по пути увеличения степени интеграции микросхем и совершенствования технологии их изготовления, привело к появлению микропроцессоров с повышенным быстродействием и разрядностью, например 16-разрядных центральных процессоров серий К588, К1801 и К1810.

Микропроцессоры, построенные на одной БИС, содержат в своем составе устройство управления, реализующее фиксированную для конкретной микросхемы систему команд, и имеют ограниченное количество внешних магистралей. Такими МПК являются 8, 16, 32-разрядные комплекты К580, K1810, К1818, которые составляют основу специализированной ЭВМ радио технических средств.

Микропроцессорная техника относится к наиболее сложным видам техники. Микропроцессорный комплект серии К1810, отличается широкой номенклатурой БИС и высоким быстродействием. Без представления о работе этих процессоров, изучение более сложных процессоров очень проблематично, их изучению уделяется очень большое внимание. Поэтому всё больше требуются специалисты по ремонту и обслуживанию комплексов автоматизации и управления, соответственно они должны знать устройство и принципы функционирования микропроцессорной техники.

Также к группе МПК можно отнести схемы, в которых устройство управления реализовано на основе программируемых логических матриц, содержащих информацию, обеспечивающую выполнение записанной в них системы команд (К587, К1811 и другие).

Сопряжение микро-ЭВМ с большинством периферийных устройств осуществляется в параллельном коде.

Одним из основных направлений в проектировании MП информационно - управляющей вычислительной системой (ИУВС) является выбор совокупности унифицированных аппаратурных, программных и конструктивных средств, необходимых для реализации алгоритмов взаимодействия различных функциональных устройств ИУВС.

1. Анализ функционирования установок для исследования режимов работы компонентов с СЭВМ

Функциональная организация интерфейсных лабораторных установок и стендов характеризует способы построения и порядок взаимодействия интерфейсных блоков.

Структура интерфейса определяется размерностью и схемой соединения, а также топологией связей. Размерность соединения - число информационных каналов и степень совмещения во времени процессов информационного взаимодействия в интерфейсе. Из-за этого существующие стандартные интерфейсы микро-ЭВМ имеют в основном одноименную структуру. Схема соединения определяет структуру информационного и управляющего каналов и сводится к последовательному, параллельному и параллельно- последовательному вариантам.

Топология связей характеризует взаимное размещение блоков ЭВМ и интерфейсных блоков в пространстве. Она зависит от конструктивного размещения плат интерфейсных блоков и разделяется на внутриблочную и межблочную.

Набор структурных параметров (размерность, схемы соединения, топологии связей) и интерфейсных операторов (функционально-независимых интерфейсных блоков, координации и другие) позволяет систематизировать возможные варианты интерфейсных лабораторных установок и стендов. При этом известно, что структурные параметры характеризуют информационный канал, а интерфейсные операторы характеризуют управляющий канал. Среди технико-экономических показателей можно выделить пропускную способность интерфейса, вместимость, надежность и стоимость лабораторной установки.

Под пропускной способностью понимается время передачи единицы информации между устройствами разрабатываемого устройства. Она зависит от времени, необходимого для установления связи, передачи единицы информации между устройствами интерфейсной лабораторной установки. Следовательно, пропускная способность зависит и от схемы соединения, топологии шин, способов реализации операторов селекции и синхронизации.

Вместимость характеризуется максимальным числом устройств, которые могут быть подключены к интерфейсу без использования дополнительных средств eё расширения. Она зависит от системы адресации приемопередающих элементов и условия конструктивной реализации. Вместимость тесно связана с остальными характеристиками интерфейсов - ее увеличение снижает значение пропускной способности и надежности и повышает стоимость разрабатываемого устройства.

Согласно современным представлениям под надежностью понимается свойство изделия (элемента, узла, устройства, машины, системы) выполнять заданные функции, сохраняя во времени свои характеристики в установленных пределах при определенных режимах и условиях использования, технического обслуживания, режимах хранения и транспортирования.

При анализе и оценке надежности какого-либо объекта приходится иметь дело со случайными событиями и величинами, что заставляет использовать понятия и методы теории вероятности.

Надежность разрабатываемого устройства определяется безотказностью, достоверностью функционирования и характеристиками обслуживаемости, в первую очередь ремонтопригодностью (восстанавливаемостью после отказов), восстанавливаемостью информации после сбоев и проверкопригодностью. (4)

Обычно оценке стоимости интерфейсной лабораторной установки включают затраты на интерфейсные блоки, систему электропитания, конструкции и кабели связи.

Для формирования требований, предъявляемых к лабораторным установкам и стендам, необходимо проанализировать имеющиеся виды интерфейсных лабораторных установок и стендов.

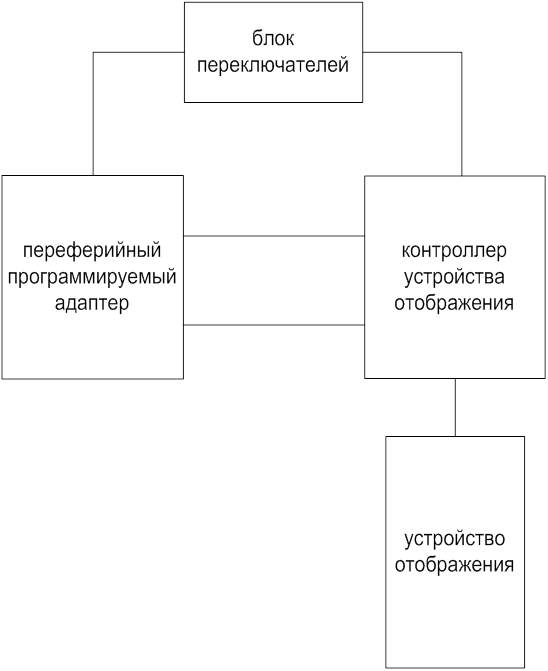

Лабораторный стенд, представленный на рисунке 1.1 предназначен для исследования параллельного интерфейса (ПИ) в ручном режиме.

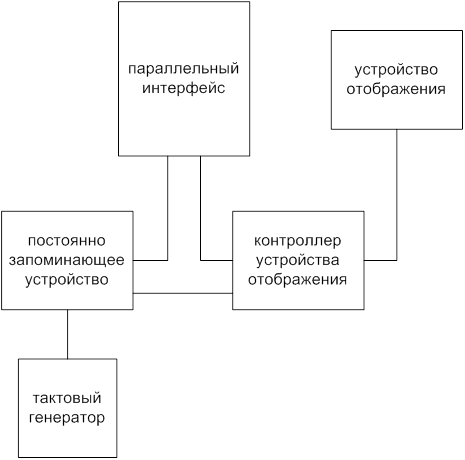

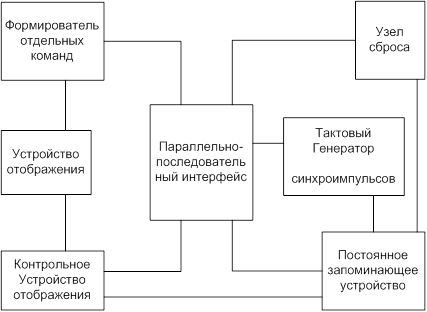

Лабораторные установки с автоматизированным режимом работы предназначена для автоматизированного выполнения лабораторных работ. Структурная схема представлена на рисунке 1.2 и включает в себя:

- Блок параллельного интерфейса (ПИ).

- Тактовый генератор (ТГ).

- Постоянное запоминающее устройство (ПЗУ).

- Контроллер устройства отображения (КУО).

- Устройство отображения (УО).

Недостатком этой лабораторной установки является то, что нет возможности проверить ПИ по отдельным командам, которые необходимы для работы ПИ в отдельных режимах.

Также недостатком является также то, что при пропуске команды, то есть в случае, если не успеть зафиксировать результат, то необходимо начинать процедуру проведения лабораторной работы заново. Также нет возможности выполнения лабораторной работы по этапам, что было возможно в лабораторной установке, рассмотренной выше, следовательно, при сбое системы необходимо программу выполнять заново.

Одним из основных представителей МПК с фиксированным набором команд является К580. (8)

Комплекс предназначен для изучения специфики построения микро-ЭВМ на базе МП БИС с фиксированным набором команд, исследования работы и методов программирования БИС.

Рисунок 1.1 - Структурная схема лабораторного оборудования для

исследования параллельного интерфейса в ручном режиме

Рисунок 1.2 - Структурная схема лабораторного оборудования для

автоматизированного выполнения лабораторных работ

2. Разработка электрической структурной, функциональной, принципиальной схем учебного комплекса по интерфейсам ввода-вывода

2.1 Разработка схемы электрической структурной учебного комплекса по интерфейсам ввода-вывода

На основе анализа существующих лабораторных установок и стендов, выдвинутых технических требований к учебному комплексу следует, что разрабатываемый учебный комплекс должен иметь универсальную структуру.

Учебный комплекс, имеющий универсальную структуру, позволяет наглядно иллюстрировать работу реальной микропроцессорной системы и состоять из нескольких лабораторных установок. К лабораторной установке с универсальной структурой можно отнести УМПК1810, структурная схема которого представлена на (рисунке 2.1). Данная лабораторная установка позволяет наглядно проследить процессы, протекающие в параллельном интерфейсе, за это отвечает блок параллельного интерфейса (БПИ), а также блок клавиатуры и дисплея (БКД). Наглядно проследить процессы, протекающие в параллельном интерфейсе, способствует подключение блока запоминающих устройств (БЗУ) и блока дешифрации адреса (БДА), что также упрощает схему.

Схема БДА построена таким образом, что сигнал разрешения работы системной магистрали выдается тогда, когда ни на резидентной, ни на канальной магистрали нет устройств, распознавших свой адрес, а также текущий цикл не является циклом обработки прерываний.

В секционируемых микропроцессорных БИС широкое применение получила открытая структура устройства. К такому типу лабораторных установок относится УМПК серии К589. (1)

Секционируемые микропроцессорные БИС представляют собой класс полупроводниковых приборов, позволяющих для каждого конкретного применения строить вычислительные устройства со структурной схемой.

Рисунок 2.1 - Структурная схема лабораторного оборудования

с универсальной структурой серии 1810

Малая разрядность микропроцессорных модулей (обычно 2, 4, 8 разрядов) открывает возможность для одного корпуса БИС формировать большое число информационных магистралей, чем в микропроцессорных комплектах с фиксированной разрядностью. Выведенные на внешние контакты микросхем магистрали секционируемых микропроцессорных БИС дают возможность разработчикам вычислительных устройств реализовать микро-ЭВМ с архитектурой, учитывающей область ее применения.

Устройство управления микро-ЭВМ на секционируемых БИС обычно выполнено в виде самостоятельного блока и может иметь различную структуру в зависимости от решаемых задач. Рабочие программы могут вводиться на языке микроопераций, при этом наилучшим образом учитываются возможности используемых микропроцессорных БИС, однако процесс программирования характеризуется повышенной трудоемкостью.

Для программирования на командном уровне устройство управления должно обеспечить реализацию системы команд и специальных команд управления, осуществляющих работу со стековой памятью и режимом прерывания.

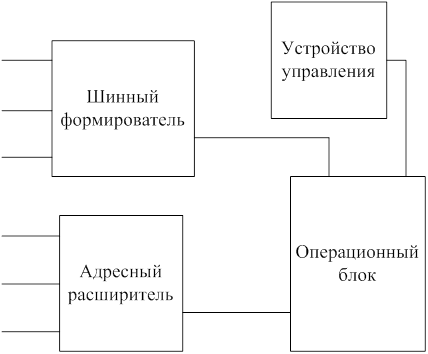

Рисунок 2.2 - Лабораторное оборудование для исследования

микропроцессорных систем серии 589

Структура универсальной конструкции, представленной на (рисунке 2.2), содержит операционный блок (ОБ), представляющий собой 8-разрядный блок обработки данных. Реализован блок на четырех БИС центрального процессорного элемента. Микропрограммное устройство управления (МУУ) входящее в структуру открытой конструкции реализовано на регистрах и обеспечивает последовательность выборки команд в соответствии с алгоритмом решаемой задачи, формирует управляющие коды для операционного блока и совокупность управляющих сигналов, обеспечивающих совместную работу блоков при выполнении команд.

Адресный расширитель (АР) предназначен для формирования 16-разрядной адресной магистрали. Шинный формирователь (ШФ) в свою очередь предназначен для формирования 8-разрядной информационной магистрали.

В данной лабораторной установке, построенной на основе секционируемых БИС МПК серии 589, существует возможность использовать в учебном процессе одни и те же внешние устройства, что и в УМПК580.

Лабораторная установка УМПК589 обладает свойством универсальности, то есть позволяет использовать внешние устройства от УМПК1801, УМПК1810. Программное обеспечение УМПК589 имеет двухуровневую структуру.

Нижний уровень представляет собой микрокоманды, реализующие систему команд однокристального микропроцессора КР580ВМ80. Верхний уровень программного обеспечения представляет собой управляющую программу, обеспечивающую согласованную работу всех блоков микро-ЭВМ процессора KP580BM80. Содержание и структура верхнего уровня программного обеспечения в УМПК589 аналогичны по назначению и содержанию управляющей программе УМПК580. Лабораторные установки, имеющие открытую структуру, обладают свойством универсальности.

К универсальному типу лабораторных установок, реализованных на основе БИС КМ1816ВЕ48, является УМПК1816.

Выбор серии К1816 в качестве базовой для построения комплекса обусловлен наличием в ней всех характерных особенностей, хорошим ее развитием, возможностью ее совместного использования с интерфейсами БИС серии К580, простотой реализации отладочных режимов.

Являясь специфическим оборудованием, лабораторная установка УМПК1816 удовлетворяет следующим требованиям:

- Возможность проведения экспериментов, с внутренними элементами, изучая их программирование и исследование различных режимов работы.

- Изучение методов разработки и отладки программного и схемотехнического обеспечения, а также методов отыскания неисправностей.

УМПК1816 имеет открытую структуру, позволяющую ей обладать свойством универсальности. (3)

С учетом необходимости гибкого изменения структуры и программного обеспечения в зависимости от целей и задач обучения комплекс построен на основе трех модулей.

Все модули являются функционально завершенными устройствами, позволяющими решать задачи различных этапов изучения построения микроконтроллеров на основе УМПК1816.

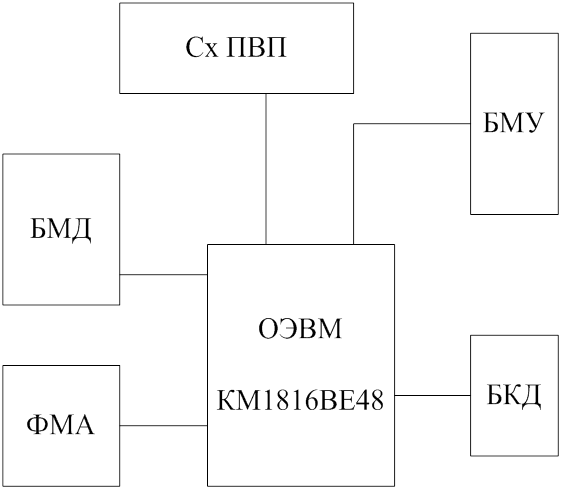

Базовый модуль (БМ) УМПК-48/ВМ, представленный на (рисунке 2.3) включает в свой состав:

- Однокристальная ЭВМ (ОЭВМ) КМ1816ВЕ48.

- Схему пошагового выполнения программ (СхПВП).

- Линии ввода-вывода (ЛВВ).

- Буферы магистралей данных (БМД).

- Буферы магистралей управления (БМУ).

- Схема формирования магистрали адреса (ФМА) для подключения внешних запоминающих устройств (ЗУ).

Использование комплекса УМПК48 в качестве базового оборудования, для проведения учебного процесса, позволяет охватить весь круг проблем разработки однокристальных ЭВМ. Учебный процесс можно условно разбить на два этапа.

Рисунок 2.3 - Структура конструкции универсального лабораторного оборудования серии 1816

На первом этапе выполняются лабораторные работы, направленные на изучение особенностей самой однокристальной ЭВМ: структуры, функционирования и программирования ее элементов (линий ввода-вывода, таймера, счетчика и так далее), временных диаграмм работы, системы команд и ориентированных на нее алгоритмов обработки информации, организации различных интерфейсных функций (параллельного и последовательного ввода-вывода данных, временных интервалов, прерываний и так далее).

На втором этапе обучения выполняется цикл работ, направленных на изучение способов расширения возможностей однокристальных ЭВМ за счет использования комплектов БИС серии 580, внешних ЗУ и тому подобное, организации отладочных режимов работы (пошаговое выполнение программ, эмуляция памяти команд), программного освоения разработки схемотехнического и программного обеспечения микроконтроллеров различных объектов, исследования способов применения кросс-средств при разработке и отладки программ для однокристальных ЭВМ, а также за счёт изучения методов отыскания неисправностей. В новом варианте комплекса, все средства, обеспечивающие возможность проведения экспериментов по исследованию функционирования однокристальных ЭВМ, и их наглядность сохранены.

Несмотря на более высокую сложность, базовое оборудование может также применяться в учебном процессе для макетирования устройств сопряжения с объектом или интерфейсом, необходимых пользователю.

Учитывая тактико-технические требования, и проведенный анализ существующих лабораторных установок, определена структура разрабатываемой лабораторной установки, приведенной на (рисунке 2.4):

- Блок параллельного-последовательного интерфейса (ППИ).

- Блок тактового генератора и синхроимпульсов (ТГиС).

- Узел сброса (УС).

- Блок постоянного запоминающего устройства (ШУ).

- Контроллер устройства отображения (КУО).

- Блок клавиатуры и отображения (БКО).

- Формирователь отдельных команд (ФОК).

Состав данного учебного комплекса соответствует тактико-техническим требованиям к лабораторным установкам.

В ПЗУ зашита программа, которая включает в себя набор заданий для реализации определенных процедур. Программа позволяет выполнять задания для исследования параллельного интерфейса в ручном и автоматизированном режимах управления.

Рисунок 2.4 - Структурная схема учебного комплекса для исследования режимов работы параллельного - последовательного

интерфейса

Для выборки команд из ПЗУ служит блок ТГиС, который включает в себя тактовый генератор и схему образования синхроимпульсов. Тактовый генератор служит для обеспечения тактируемыми импульсами лабораторную установку при ее работе в автоматизированном режиме. Одиночные синхроимпульсы применяются для работы в ручном режиме, при выборе одиночных команд и при работе в режиме с определенным набором команд.

Блок ППИ включает в себя параллельный и последовательный интерфейс и систему обеспечения его работы.

Контроллер устройства отображения обеспечивает правильное и безошибочное отображение информации на индикаторном табло или на светодиодах.

Устройство отображения предназначено для отображения сигналов и включает в себя два блока индикации. Первый блок индикации предназначен для визуального отображения состояний выходов логических схем. Данный блок содержит две линейки светодиодов: линейку А и линейку В. Второй блок индикации предназначен для отображения информации в виде цифр.

Формирователь отдельных команд необходим при проведении лабораторных работ, связанных с определенным типом команд.

Узел сброса позволяет вернуть всю лабораторную установку в исходное, то есть в нулевое состояние. Основные узлы лабораторной установки имеют входы, возвращающие их в исходное состояние. Это вызвано несколькими причинами:

- Ошибка оператора при проведении исследований.

- Сброс системы при завершении работы.

- Сброс системы при обнаружении неисправностей в ППИ.

В состав набора расширительных модулей при необходимости могут быть включены самостоятельно разработанные устройства сопряжения с различными объектами. Это позволяет выполнить ряд лабораторных работ по изучению программного и схемотехнического обеспечения специализированных узлов.

В силу универсальности нового варианта базового оборудования учебной лабораторной установки она может одинаково эффективно применяться как в учебном процессе, так и при проведении научно-исследовательских и опытно-конструкторских работ.

В результате проведенного анализа, существующих схем лабораторных установок для исследования режимов работы ППИ, следует:

- Существующие типы лабораторных установок имеют универсальную конструкцию.

- На основе проведённого анализа структурных схем лабораторных установок универсальной конструкции, разработана лабораторная установка, которая удовлетворяет предъявленным техническим требованиям к лабораторным установкам.

- Данный учебный комплекс должен содержать в своем составе набор блоков, позволяющий ей работать в автоматизированном и ручном режимах, а так же позволять выполнять лабораторные работы с определенным набором команд.

В разработанной структурной схеме центровым элементом является блок ППИ, являющегося основой структурной схемы. В этом блоке ППИ функционирует постоянно. Расположение блока аргументируется тем, что цель работы заключается в исследовании ППИ.

2.2 Разработка схемы электрической функциональной учебного комплекса по интерфейсам ввода-вывода

Состав структурной схемы назначение составляющих структурную схему блоков позволяет разработать функциональную схему учебного комплекса. Функционально учебный комплекс можно разбить на два блока:

- устройство для исследования режимов функционирования параллельного интерфейса (первый блок);

- устройство для исследования режимов функционирования последовательного интерфейса (второй блок).

Из структурной схемы следует, что основа структурной схемы является устройства для исследования режимов функционирования параллельного интерфейса является блок параллельный периферийный адаптер (ППА), в котором он функционирует постоянно.

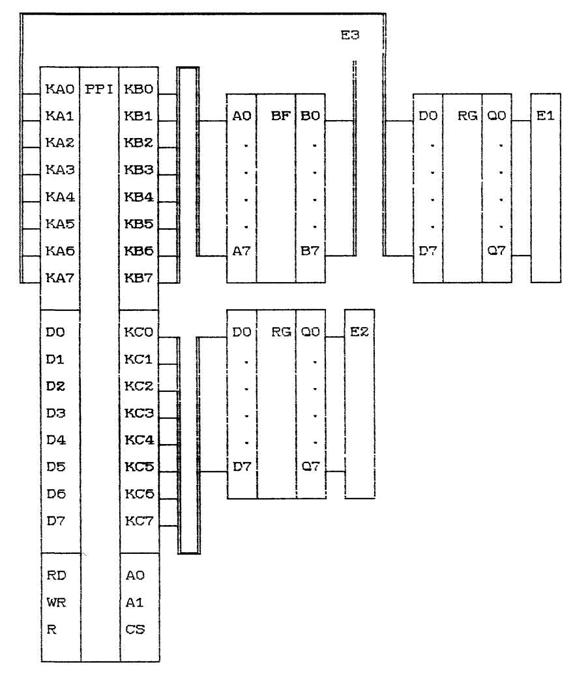

В УМПК580 основой модуля является БИС параллельного периферийного адаптера (ППА). Каналы ППА подключены к схемам индикации и наборным полям через регистры и буфер. Это позволяет отключить их с помощью переключателя и использовать каналы для сопряжения микро-ЭВМ с устройствами ввода-вывода (УВВ). Функциональная схема данного блока приведена на (рисунке 2.5).

Иной подход к этому блоку осуществлен в УМПК1810. Блок параллельного интерфейса, представленный на (рисунке 6), собран на основе БИС КР580ВВ55.

Для усиления его сигналов используются два буфера и регистр. Схема позволяет пользователю применять каналы А и Б как для ввода, так и для вывода информации.

Проведя анализ первого блока, следует вывод, что в нем учебного для осуществления исследований режимов работ периферийного

адаптера достаточно подключить периферийный адаптер через буферы, которые имеют три состояния. Это вызвано тем, что даётся возможность изменять загружаемость адаптера. При необходимости буферный усилитель отключает канал, неиспользуемый в работе, тем самым разгружает общую шину и увеличивает быстродействие устройства.

Рисунок 2.5- Функциональная электрическая схема блока ППА УПМК580

Рисунок 2.6- Функциональная электрическая схема блока параллельного интерфейса УМПК 1810

При работе первого блока в автоматизированном режиме программы на выполнение записаны в постоянном запоминающем устройстве в блоке ПЗУ.

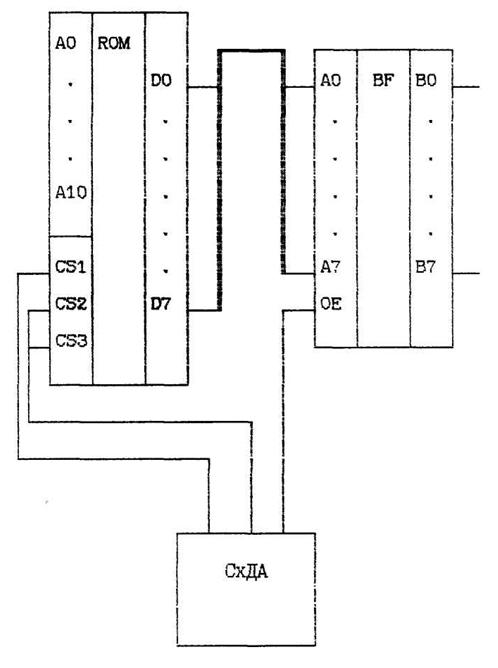

В УМПК580 блок запоминающих устройств, представленный на (рисунке 2.7) содержит: ПЗУ, буфер и схему дешифрации адреса (СхДА).

Дешифратор адреса формирует сигналы выборки ПЗУ. При обращении к ячейкам памяти СхДА выдает сигнал, открывающий буфер. При замыкании переключателя SA можно запретить работу ПЗУ, например для изучения методов отыскания неисправностей или для подключения внешних ЗУ.

Учитывая специфику работы разрабатываемого устройства, следует, что состав блока ПЗУ будет включать в себя только схему ПЗУ и сигнал выборки от блока ТГиС, так как нет необходимости производить выборку программ. Программы считываются из ОЗУ последовательно, в порядке, установленном при записи в ПЗУ. В состав блока ТГиС входит тактовый генератор и схема одновибратора. Состав схемы тактового генератора входит два элемента ИЛИ-НЕ, которые связывают кварц ZQ1 с 4-разрядным двоичным счетчиком.

Соединение входов и выходов счетчика по определенной схеме позволяет иметь информацию о делении частоты кварца на 2, 4, 8 и 16.

При работе схемы в ручном режиме за синхросигнал отвечает блок синхроимпульсов, входящий в блок ТГиС. За формирование синхроимпульса отвечает схема одновибратора. В схеме на двух ждущих мультивибраторах с возможностью перезапуска, свойственно, что в каждом мультивибраторе есть два входа запуска: с активным высоким уровнем и с активным низким уровнем.

Программа, вводимая в ППА, и результаты проведения работы отображаются на индикаторном табло в блоке устройств отображения. Данный блок состоит из цифрового индикатора и двух линеек светодиодов. Это связано с тем, что необходимо контролировать входную и выходную информацию ППА.

Блок индикации 1 предназначен для визуального отображения состояний входов логических схем. Светодиоды, содержащиеся в блоке индикации 1 обеих линеек, управляются интегральными микросхемами, содержащими инверторы с открытым коллекторным выходом. В соответствии с этим светодиод будет светиться в том случае, если на входе инвертора находится логическая “1”. Если на входе инвертора логический “0”, то светодиод не будет светиться. В целях снижения нагрузки на источник питания линейки светодиодов записываются независимо друг от друга, а в целях снижения нагрузки шины, светодиоды подключены через буферы, имеющие три состояния.

Рисунок 2.7- Функциональная электрическая схема блока ПЗУ УМПК580

Блок индикации 2 предназначен для отображения информации в виде цифр. Он состоит из полупроводникового сегментного индикатора. Данный индикатор также подсоединен к общей шине через буферы для разгрузки шины при не использовании индикатора.

Данный индикатор может не использоваться при ручном режиме работы.

За работой индикаторного табло следит блок контроллеров устройства отображения. Данный блок включает в себя регистр с восемью тактируемыми триггерами, так как в цифровом табло восемь входов, и восемью сопротивлениями на выходе для ограничения тока.

Схема сброса представляет собой диодную схему срабатывания при включении питания. При этом вырабатывается сигнал, который приводит схему в исходное состояние.

Формирователь отдельных команд представляет собой набор переключателей и схему формирования сигналов без дребезга.

Формирователи сигналов без дребезга предназначены для формирования "чистых" положительных и отрицательных перепадов напряжения.

2.3 Выбор элементной базы

При разработке микропроцессорных устройств и периферийного оборудования ЭВМ необходимо выбрать ИМС определенных серий, которые бы наиболее полно удовлетворяли требованиям, предъявляемым к разрабатываемому устройству. Удачное применение при оценке качества выбранной серии микросхем нашла методика оценки и выбора ИМС по минимальному критерию качества.

Уровень миниатюризации является количественной мерой совокупности технологических решений, направленных на эффективное использование объема, массы и потребляемой аппаратурой энергией при обеспечении характеристик, определяющих пригодность ее применения заданному назначению.

Уровень миниатюризации РЭА являются:

- Соответствие современному техническому уровню микроэлектронных изделий.

- Соответствие применяемых в РЭА изделий современному уровню миниатюризации аппаратуры.

- Техническая совместимость других изделий электронной техники с интегральными микросхемами (ИМС).

Развитие микроэлектроники способствовало появлению малогабаритных, высоконадежных и экономичных вычислительных устройств на основе цифровых микросхем. Требование увеличения быстродействия и уменьшения мощности потребления вычислительных средств привело к созданию серий цифровых микросхем. Серия представляет собой комплект микросхем, имеющих единое конструктивно-технологическое исполнение. К таким сериям относятся серии К155, К555.

За годы развития цифровых микросхем базовые электронные ключи развивались в следующей последовательности:

- Интегральная инжекторная логика (ИИЛ).

- Резисторно-транзисторная логика (РТЛ).

- Резисторно-емкостная транзисторная логика (РЕТЛ).

- Диодно-транзисторная логика (ДТЛ).

- Транзисторно-транзисторная логика (ТТЛ).

- Эмиттерно-связанная логика (ЭСЛ).

- Транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ).

Проанализировав существующие функциональные узлы различных устройств показал, что:

- Для создания функциональной схемы лабораторного оборудования следует опираться на структурную схему устройства. Каждый блок структурной схемы должен быть разбит на функционально-законченные узлы. Функциональная схема в себя включает: блок ПИ, блок ПЗУ, блок выборки программ, тактовый генератор, схему одновибратора, индикаторное табло и линейки светодиодов, диодную схему сброса, формирователь сигналов без дребезга.

- Назначение функциональных блоков должно основываться на режимах работы разрабатываемого лабораторного оборудования и принципах функционирования отдельных ее узлов.

Целесообразно для разработки устройства использовать ИМС серий К155, К555, совместимых по техническим параметрам с серией К580.

2.4 Разработка схемы электрической принципиальной учебного комплекса по интерфейсам ввода-вывода

Функционирование микросхемы КР580ВВ55

Основой разрабатываемой лабораторной установки является параллельный интерфейс.

Асинхронный процесс обмена данными между микро-ЭВМ и внешними устройствами (ВУ), а также требования наиболее рационального распределения времени работы микро-ЭВМ приводят к разработке интерфейсных устройств необходимых при организации обмена данными.

Задача таких устройств состоит в приеме данных по сигналам управления, формирования сигналов, указывающих на наличие данных в устройстве, выдаче данных по сигналам управления, а также формировании сигналов, указывающих на готовность устройства к приему новых данных.

Процесс обмена информацией организуется интерфейсным устройством под действием сигналов управления, поступающих от микро-ЭВМ и ВУ.

Технология больших интегральных схем (БИС) позволяет создавать универсальные многофункциональные интерфейсные устройства ввода-вывода параллельной информации.

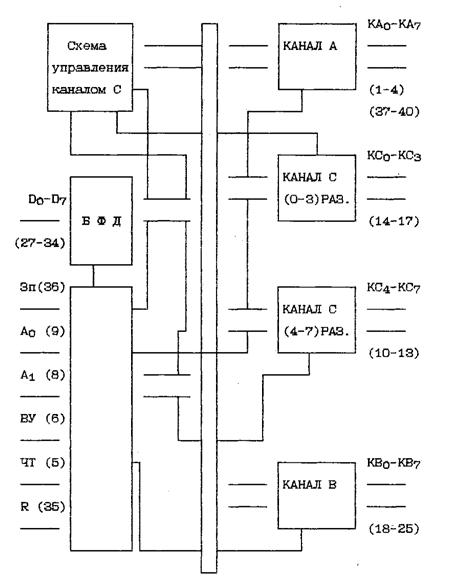

Такие устройства могут быть программируемыми и применяться для двунаправленной передачи данных и сигналов управления. Микро-ЭВМ информируется о готовности устройства к обмену данными, как правило, по сигналам прерывания. Обмен данными осуществляется путем обращения микро-ЭВМ к устройству ввода-вывода как к адресу памяти или ВУ. Таким образом, интерфейсные устройства ввода-вывода параллельной информации позволяют согласовать во времени процесс обмена данными между ВУ и микро-ЭВМ при рациональном использовании времени работы микро-ЭВМ. Микросхема КР580ВВ55 представляет собой программируемое устройство, используемое для ввода-вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам: А, В, С. Направление обмена и режим работы для каждого канала задается программно. Каналы служат для передачи, как данных, так и управляющих сигналов. Структура микросхемы КР580ВВ55 приведена на рисунке 2.8.

Назначение выводов:

Д0 - Д7 - двунаправленная магистраль данных для передачи данных, управляющих слов и информации состояния.

КА 0- КА 7 - двунаправленная магистраль данных канала А.

КВ 0 - KB 7 - двунаправленная магистраль данных канала В.

КС 0 - КС 7 - двунаправленная магистраль данных канала С.

(магистрали каналов передачи данных, управляющих сигналов и сигналов запроса на прерывание от ВУ и МП БИС).

ВУ - выбор устройства.

Для микро-ЭВМ схему можно представить состоящей либо из четырех ВУ, либо из четырех адресов памяти.

Для формирования сигнала выборки устройства, подаваемого на вход ВУ, можно использовать шины А 0 - A 15 MA микро-ЭВМ. При обращении к схеме как к четырем ВУ входы Чт и Зп должны быть подключены к шинам Чт. ВВ и Зп. ВВ ВУ микро-ЭВМ.

При обращении к схеме как к четырем адресам памяти ее входы Чт и Зп должны быть соответственно подключены к шинам Чт. ПАМЯТЬ и Зп. ПАМЯТЬ микро-ЭВМ.

Схема выполняет следующие функции: буферизацию (при асинхронном режиме обмена данными) и преобразование формата данных.

Режимы работы микросхемы КР580ВВ55 задаются при ее начальной установке. Четыре под адресных регистра схемы включают в себя три регистра каналов ввода-вывода данных (А, В, С) и регистр управления. Регистр канала С может быть подразделен на два четырехразрядных регистра ввода-вывода данных, к которым осуществляется доступ как к отдельным независимым регистрам (рисунок2.8).

Существует возможность подразделения трех каналов на две группы. В этих группах каналы А и В используются для обмена данными с микро-ЭВМ, а отдельные шины канала С - для записи управляющих сигналов.

Режимы работы каналов задаются путем записи управляющего слова в регистр управления.

Существует три типа работы схемы:

Тип 0. Это простой ввод-вывод данных по трем 8-разрядным каналам, причем канал С может быть подразделен на два 4-разрядных канала. Каждый из каналов может быть использован отдельно для ввода или вывода информации. При работе схемы в этом режиме никаких дополнительных сигналов управления не требуется.

Тип 1. Позволяет осуществлять обмен данными по каналам А и В с помощью сигналов управления, передаваемых по каналу С. Для каналов А и В существует четыре комбинации взаимных направлений передачи данных:

- Каналы А и В работают в режиме вывода данных.

- Каналы А и В работают в режиме ввода данных.

- Канал А работает в режиме ввода, а В - в режиме вывода данных.

- Канал А работает в режиме вывода, а В - в режиме ввода данных.

Рисунок 2.8- Структурная схема КР580ВВ55

Незадействованные для управляющих сигналов шины канала С могут быть использованы для ввода-вывода информации. Направление передачи информации по этим шинам определяется управляющим словом, записанным в регистре управления. (5)

В ходе рассмотрения существующих типов микросхем можно сделать вывод: анализируя сравнительные характеристики микросхем различных серий, среди многообразия типов и серий микросхем, выявлено, что наиболее подходящими элементами для устройства являются микросхемы серий 155, 555, 530, 533, 531, 555. Уровни питающих напряжений, а также уровни напряжений логических сигналов позволяют применять данные микросхемы в разрабатываемом учебном комплексе.

В ходе анализа существующих типов и серий микросхем постоянной памяти выявлено, что для разрабатываемой лабораторной установки наиболее подходит постоянная память типа РПЗУ серии 573, так как она обладает свойством перепрограммирования.

Таким образом, интерфейсные устройства ввода-вывода параллельной информации позволяют согласовать во времени процесс обмена данными между ВУ и микро-ЭВМ при рациональном использовании времени работы микро-ЭВМ. Микросхема КР580ВВ55 представляет собой программируемое устройство, используемое для ввода-вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам: А, В, С. Направление обмена и режим работы для каждого канала задается программно. Каналы служат для передачи, как данных, так и управляющих сигналов.

Заключение

Исходя из анализа существующих структур лабораторных установок и стендов, функционального состава отдельных блоков, а также многообразия типов и видов микросхем следует:

1. Разрабатываемый учебный комплекс должен обладать наилучшими свойствами уже существующих типов лабораторных установок, которые имеют универсальную конструкцию, позволяющую наглядно иллюстрировать работу реальной микропроцессорной системы.

2. На основе анализа структурных схем лабораторных установок универсальной конструкции разработан учебный комплекс, удовлетворяющая предъявленным требованиям, которыми являются простота, малая стоимость, доступность.

3. Первый блок учебного комплекса содержит в своем составе следующие блоки: блок параллельного интерфейса (ПИ), блок тактового генератора и синхроимпульсов С ТГиС), узел сброса (УС), блок постоянного запоминающего устройства (ПЗУ), контроллер устройства отображения (КУО), блок клавиатуры и отображения (БКО), формирователь отдельных команд (ФОК), позволяющей работать в автоматизированном и ручном режимах.

4. Второй блок учебного комплекса содержит в своем составе следующие блоки: блок последовательного интерфейса (УСАПП), блок постоянного запоминающего устройства (ПЗУ), контроллер пр