Синтез цифрового автомата управления памятью

В соответствии с заданием в данном курсовом проекте необходимо синтезировать цифровой автомат. После нажатия кнопки ПУСК эта схема должна обеспечить формирование заданного количества выходных сигналов в соответствии с задание на расчет.

Разработка принципиальной схемы производится при помощи метода синтеза цифровых схем по методу Карт Карно.

В заключении приведены меры по обеспечению защиты от внешних электромагнитных помех.

В работе приведены все указанные в задание принципиальные схемы, временные диаграммы и эскизы печатных плат.

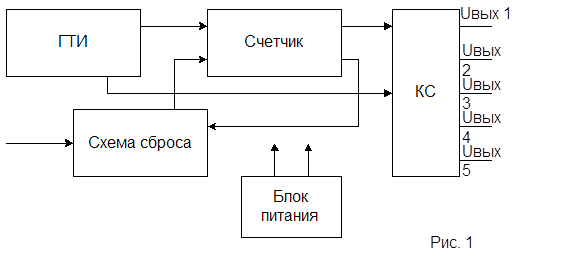

1. РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ УСТРОЙСТВА

Структурная схема представляет собой своеобразный макет , по которому в ходе разработки будет спроектировано устройство управления ПЗУ. Он определяет основные блоки проектируемого устройства и то, как эти блоки будут взаимодействовать между собой.

В соответствии с заданием разрабатываемое устройство должно выдавать на пяти выходах периодические последовательности цифровых сигналов вида:

| Выход 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Выход 2 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| Выход 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| Выход 4 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| Выход 5 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

Частота следования выходных импульсов 10 МГц

Синтезируемая схема должна содержать: генератор тактовых импульсов, счетную схему считающую с периодом 30 тактовых импульсов, комбинационную схему.

Принцип работы синтезируемого устройства заключается в следующем: С генератора тактовых импульсов (ГТИ) импульсы заданной частоты (19 МГц) поступают на счетную схему (Сч). Последовательность работы счетной схемы соответствует заданию, т.е. счетчик считает поступающие тактовые импульсы до 30, затем происходит сброс счетчика в нулевое состояние и счет повторяется заново. Со счетной схемы сигналы поступают на комбинационную схему (КС). Данный преобразователь (комбинационная схема) формирует на пяти выходах заданные последовательности импульсов. После 30 тактовых интервалов счетчик обнуляется, на выходе появляется первое значение последовательности и период выходных импульсов повторяется.

Таким образом получили схему, которая точно выполняет заданные условия работы.

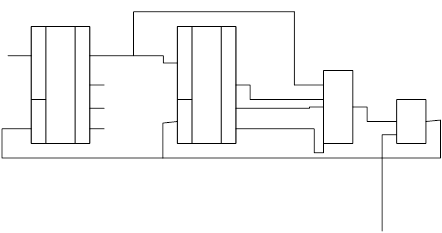

Функциональная схема синтезируемого устройства представлена на рисунке 1.

В соответствии с заданием базовые элементы - определяются по выбору, по этому выбираем элементы ТТЛШ как наиболее высокочастотные по сравнению с другими типами логических элементов. Определим, что разрабатываемое устройство будет состоять из элементов серии К555.

У микросхем данной серии следующие особенности:

- потребляемая мощность, не более – 7 мВт

- напряжение источника питания – 5 В

- Задержка распространения сигнала, не более – 20 нс

- Максимальная частота – 80 МГц

- Коэффициент разветвления, не более – 10

Логические элементы разрабатываем в базисе И-НЕ.

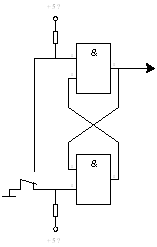

В качестве дополнительных условий к разрабатываемой схеме предъявляются требования – разрабатываемая система должна быть синхронной, т.е требуется провести дополнительные мероприятия по синхронизации выходов схемы. Для этого на выходах схемы предусмотрим разрешение выдачи сигнала. при условии наличия синхросигнала с ГТИ. Данное схемное решение осуществляем при помощи логической операции И.

Таким образом функциональная зависимость сигнала выхода от сигнала синхронизации представляется как (представим сразу в базисе И-НЕ):

ВЫХ=Вых С=Вых С

Далее рассмотрим синтез каждого устройства отдельно и более подробно.

2. СИНТЕЗ И РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ

Одной из важнейших задач синтеза принципиальных схем на ИМС является минимизация количества микросхем и числа их соединений. Не менее важным условием синтеза является максимальное использование элементов с одинаковыми функциями.

Задающий генератор

Электрический импульсом называют ток или напряжение, действующий в течении ограниченного промежутка времени меньше или соизмеримого с длительностью переходных процессов в электрических цепях. В радиотехнике и технике связи используют импульсы различной формы. Прямоугольные импульсы более развились и на практике чаще применяют именно импульсные последовательности.

Генератор импульсов‑ автогенератор ,вырабатывающий импульсы прямоугольной формы. Генераторы обеспечивают работу цифрового устройства и характеризуются частотой сигнала, стабильностью частоты, скважностью, видом последовательности сигнала и другими параметрами.

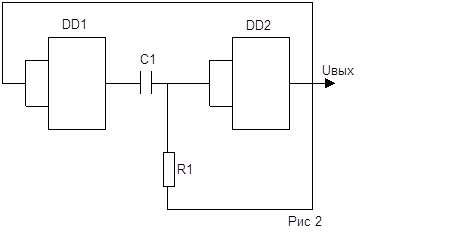

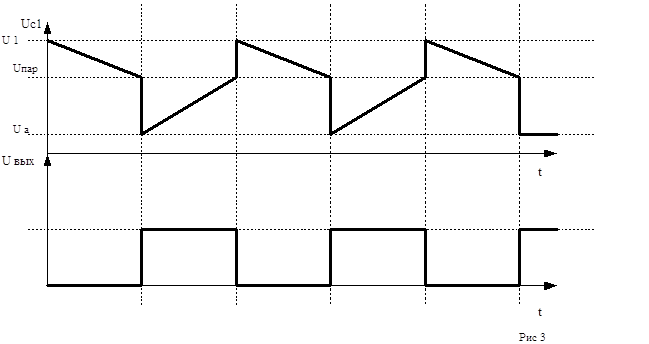

В соответствии с принятыми условиями необходимо разработать схему ГТИ и рассчитать его элементы в базисе И-НЕ. Принципиальная схема мультивибратора в автоколебательном режиме приведена на рисунке 2. На рисунке 3 показана временная диаграмма позволяет более полно судить о роботе ГТИ и детально разобрать принцип его работы.

Принцип работы приведенной выше схемы наглядно демонстрирует временная диаграмма. Разрабатываемый мультивибратор в автоколебательном режиме. В те моменты времени, когда напряжение на входе DD2 достигает порогового значения схема переводится в противоположное состояние и на выходе изменяется состояние с 0 в 1 или наоборот. Время нахождения схемы как в одном, так и в другом состоянии определяется параметрами элементов времязадающей RC – цепочки.

Для регулирования длительности данных импульсов и пауз ниже произведен расчет параметров схемы.

Пусть генератор работает с заданной частотой выхода.

Тогда:

Исходные значения

![]() Гц – частота ГТИ

Гц – частота ГТИ

Q = 10 исходная скважность ГТИ

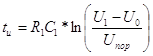

уравнение определяющее длительность выходного импульса

уравнение определяющее длительность выходного импульса

где, U1=3.6 В - уровень логической 1 для элемента ТТЛШ

U0=0.4 В - уровень логической 0 для элемента ТТЛШ

Uпор=1.8 В – пороговое напряжение для элемента ТТЛШ

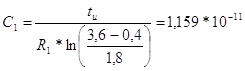

![]() с - значение периода следования импульсов ГТИ

с - значение периода следования импульсов ГТИ

![]() с - значение длительности импульса

с - значение длительности импульса

![]() с - длительность паузы

с - длительность паузы

Для достижения данных параметров длительность импульса и паузы определяем значением емкости и сопротивления.

![]()

R1=1000 Ом – значение сопротивления резистора (выбираем произвольно)

Ф – рассчитанное значение емкости исходя из длительности импульса.

Ф – рассчитанное значение емкости исходя из длительности импульса.

С1= 10*10-12 Ф – выбранное значение емкости

![]() с – уточненное значение длительности импульса

с – уточненное значение длительности импульса

![]() с – уточненное значение длительности паузы

с – уточненное значение длительности паузы

3. Счетная схема

С выхода генератора имеем сигнал частотой 10 МГц.

В соответствии с особенностью работы разрабатываемого устройства необходимо произвести подсчет импульсов лишь 30 раз, а затем произвести сброс счетчика и повторять данную операцию в периоде. Поэтому разрабатываем не типовой делитель на 30.

В качестве делителя частоты на 30 используем счетчик К555ИЕ7 (с коэффициентом пересчета – 16) дополненный элементом И-НЕ которые выдают на выходе логическую 1 по заданному фронту 30 импульса и сбрасывают счетчик в ноль.

Произведем синтез данной схемы счетчика.

В таблице 3.1 приведены зависимости функционирования счетчика выбранного типа. В данной таблице приведены возможные варианты входных комбинаций и соответствующие выходные сигналы:

Таблица 3.1

| Вход счета С | Вход сброса R | Выход 1 | Выход 2 | Выход 4 | Выход 8 |

| 0 | 1 | n-1 | n-1 | n-1 | n-1 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 |

![]()

![]()

Условное обозначение счетчика показано на рисунке 4

Условное обозначение счетчика деления частоты на 30

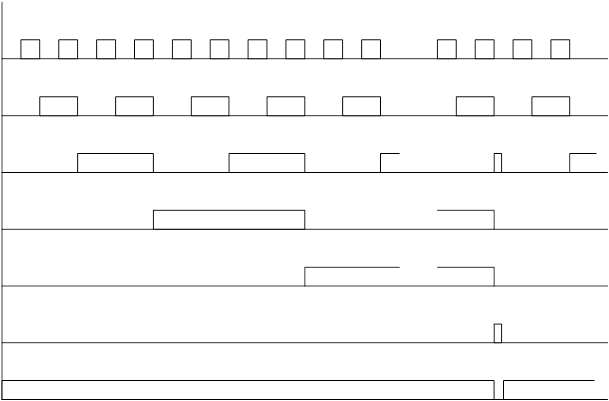

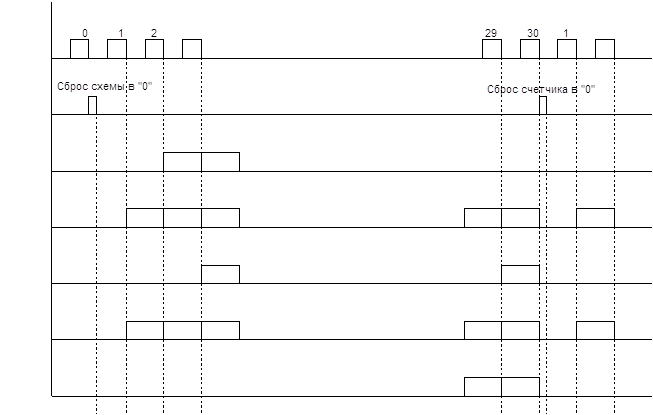

Временная диаграмма работы счетчика представлена на рисунке 5

4. Комбинационная схема

С выходов счетной схемы код передается на входы преобразователя. Следует заметить, что выходы счетной схемы ![]() - соответствуют входам : a, b,c,d,e.

- соответствуют входам : a, b,c,d,e.

Составим общую таблицу истинности для каждого выхода синтезируемого устройства. Для всех выходов будут функции 5 переменных, т.к счет необходимо производить до 30 импульсов, а пяти переменным соответствует старшее число – 31 (с учетом нулевого состояния)

Таким образом комбинационная схема (преобразователь) преобразует значения пяти функций входа в пять функций выхода:

Таблица 4.1

Преобразование переменных a, b,c,d,e в функции выхода

| e | d | C | b | a | Uвых 1 | Uвых 2 | Uвых 3 | Uвых 4 | Uвых 5 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 3 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 4 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 5 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

| 6 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 7 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 9 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 10 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 11 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 12 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 13 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| 14 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 15 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 16 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| 17 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

| 18 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 19 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| 20 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 21 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| 22 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 23 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 24 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 25 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| 26 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 27 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 28 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 29 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

Осуществим минимизацию функций выхода методом карт Карно. При минимизации методом карт Карно выделения осуществляем с помощью выделения рамками.

| ba\dc | 00 | 01 | 11 |

| ba\dc |

| 01 | 11 | 10 | |||

| 00 | 1 | 1 | 00 | 1 | 1 | |||||||

| 01 | 1 |

| 1 | 01 | 1 | 1 | ||||||

| 11 | 1 | 1 | 11 |

| X | |||||||

| 10 | 1 | 1 | 1 | 10 | 1 | X |

Uвых1=cde v ade v abce v abcde v abce v bde v abce

| ba\dc |

| 01 | 11 | 10 | ba\dc |

| 01 |

| 10 | |||

| 1 | 00 | 1 | 1 | 1 | |||||||

| 1 | 1 |

| 01 | 1 |

| 1 | 1 | ||||

| 11 | 1 | 1 | 1 | 1 | 11 | 1 | X | |||||

| 10 | 1 | 1 | 10 |

| X | 1 |

Uвых2=cde v ade v abe v bcde v bcde v bce v bde v abde

| ba\dc | 00 |

| 11 | 10 | ba\dc | 00 | 01 | 11 | 10 | |||

| 00 | 1 |

| 00 |

| ||||||||

| 01 |

| 1 |

| 1 | 01 |

|

| 1 | ||||

| 11 | 1 | 1 | 11 | 1 | 1 | X | 1 | |||||

| 10 |

| 1 | 1 | 10 | 1 | X | 1 |

Uвых3=bcd v abde v bcde v abde v bcde v ace v bde

| ba\dc |

|

| 11 | 10 | ba\dc | 00 |

|

| 10 | |||

| 00 | 1 | 1 | 1 | 1 | 00 | 1 | 1 | 1 | ||||

| 01 | 1 | 1 | 1 |

| 01 |

| 1 | 1 | 1 | |||

| 11 |

| 1 | 1 | 11 | 1 | X | ||||||

| 10 | 1 |

| 1 | 10 |

| 1 |

Uвых4=bde v abde v bс v dce v abce v abde v abcde v abcde v bde v abde

| ba\dc | 00 | 01 | 11 | 10 | ba\dc |

| 01 |

| 10 | |||

| 00 |

| 00 |

| 1 | ||||||||

| 01 | 1 | 01 | 1 |

| 1 | |||||||

| 11 | 1 |

| 1 |

| X | 1 | ||||||

| 10 | 1 | 1 | 1 | 10 | 1 | 1 | X | 1 |

Uвых5=abce v abce v abde v acde v acde v bcde v abde v abe v cde v bde

Представим функции в базисе И-НЕ:

Uвых1=cde v ade v abce v abcde v abce v bde v abce

Uвых2=cde v ade v abe v bcde v bcde v bce v bde v abde

Uвых3=bcd v abde v bcde v abde v bcde v ace v bde

Uвых4=bde v abde v bс v dce v abce v abde v abcde v abcde v bde v abde

Uвых5=abce v abce v abde v acde v bcde v abde v abe v cde v bde

5. Схема сброса

Для устойчивой работы при необходимости, необходимо произвести сброс схемы в исходной в одно из заданных состояний (например в 0). Сброс будем производить при помощи кнопки сброса и логических элементов.

Схема сброса представлена на рисунке 6

рис. 6

Принципиальная схема всего синтезируемого генератора цифровых сигналов представлена на рисунке 7.

Временная диаграмма работы данной схемы приведена на рисунке 8

рис. 8

ЗАКЛЮЧЕНИЕ

В соответствии с техническим заданием, в данном курсовом проекте было разработано устройство, формирующее последовательность цифровых сигналов для управления постоянным запоминающим устройством. Выполнение данной работы включало в себя все основные этапы проектирования цифровых устройств на интегральных микросхемах. Это позволило получить и закрепить практические навыки разработки структурной схемы устройства, синтеза и разработки его принципиальной схемы, конструктивной проработки изделия.

В заключении хотелось бы отметить, что разработанное устройство, а особенно формирователи выходных последовательностей оказались достаточно сложными и содержат большое количество корпусов интегральных микросхем.

00

00 00

00 11

11 00

00

01

01

1

1 1

1

00

00

01

01 11

11

1

1