Дифференциальный усилитель

Московский Государственный Авиационный Институт(Технический Университет)

Пояснительная записка

к курсовому проекту по курсу "Технология аппаратуры САУ".

Дифференциальный усилитель.

Выполнил студент группы

Консультант: / /

Принял преподаватель: / /

Москва, 1995 год.

Содержание:

- Техническое задание...............................................3

- Анализ технического задания................................6

- Выбор материалов, расчет элементов..................6

- Выбор подложки......................................................8

- Технологический маршрут.....................................8

- Выбор корпуса ГИС................................................8

- Оценка надежности.................................................9

- Список литературы.................................................11

Задание

на разработку гибридной интегральной микросхемы (ГИС) частного применения.

Дифференциальный усилитель.

Дифференциальный усилитель предназначен для усиления сигналов постоянного тока или в качестве усилителя сигналов низкой частоты.

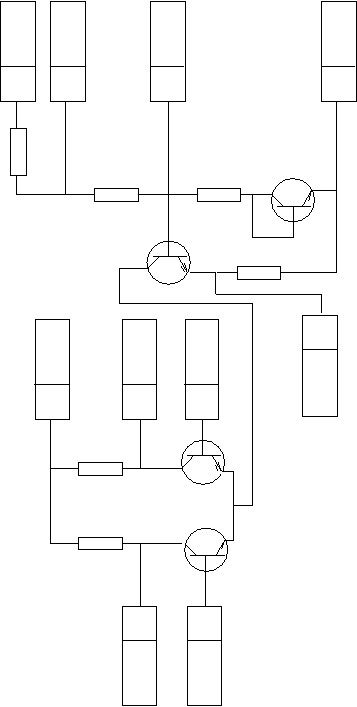

Схема электрическая принципиальная:

Смотрите на следующей странице (рисунок 1).

Рисунок 1 : Схема электрическая принципиальная

Технические требования:

Микросхема должна соответствовать общим техническим требованиям и удовлетворять следующим условиям:

- повышенная предельная температура +85°С;

- интервал рабочих температур -20°С...+80°С;

- время работы 8000 часов;

- вибрация с частотой до 100 Гц, минимальное ускорение 4G;

- линейное ускорение до 15G.

Исходные данные для проектирования:

- Технологический процесс разработать для серийного производства с объёмом выпуска – 18000 штук.

- Конструкцию ГИС выполнить в соответствии с принципиальной электрической схемой с применением тонкоплёночной технологии в одном корпусе.

- Значения параметров:

Позиционное обозначение: | Наименование: | Количество: | Примечание: |

R1,R3,R5 | резистор 4КОм±10% | 3 | Р=3,4мВт |

R2 | резистор 1,8КОм±10% | 1 | Р2=5,8мВт |

R4 | резистор 1,7КОм±10% | 1 | Р4=2,2мВт |

R6 | резистор 5,7ком±10% | 1 | Р6=2,6мВт |

VT1,VT4 | транзистор КТ318В | 2 | Р=8мВт |

VT2 | транзистор КТ369А | 1 | Р=14мВт |

VT3 | транзистор КТ354Б | 1 | Р=7мВт |

Напряжение источника питания: 6,3 В±10%.

Сопротивление нагрузки не менее: 20 КОм.

1. Анализ технического задания.

Гибридные ИМС (ГИС) – это интегральные схемы, в которых применяются плёночные пассивные элементы и навесные элементы (резисторы, конденсаторы, диоды, оптроны, транзисторы), называемые компонентами ГИС. Электрические связи между элементами и компонентами осуществляются с помощью плёночного или проволочного монтажа. Реализация функциональных элементов в виде ГИС экономически целесообразна при выпуске малыми сериями специализированных вычислительных устройств и другой аппаратуры.

Высоких требований к точности элементов в ТЗ нет.

Условия эксплуатации изделия нормальные.

2. Выбор материалов, расчёт элементов, выбор навесных компонентов.

В качестве материала подложки выберем ситалл СТ50-1.

Транзисторы выберем как навесные компоненты.

VT1,VT4-КТ318В,

VT2-КТ369А,

VT3-КТ354Б.

По мощностным параметрам транзисторы удовлетворяют ТЗ. По габаритным размерам они также подходят для использования в ГИС.

Рассчитаем плёночные резисторы.

Определим оптимальное сопротивлениеквадрата резистивной плёнки из соотношения:

ρопт=((∑Ri)/(∑1/Ri))^1/2.

ρопт=3210(Ом/).

По полученному значению выбираем в качестве материала резистивной плёнки кермет К-20С. Его параметры: ρопт=3000 ОМ/, Р0=2 Вт/см^2, αr=0.5*10^-4 1/°С.

В соответствии с соотношением

δ0rt=αr(Тmax-20°C)

δ0rt=0.00325, а допустимая погрешность коэффициента формы для наиболее точного резистора из

δ0кф= δ0r- δ0ρ- δ0rt- δ0rст- δ0rк

равно δ0кф=2.175. Значит материал кермет К-20С подходит.

Оценим форму резисторов по значению Кф из

Кфi=Ri/ρопт.

Кф1,3,5=1.333, Кф2=0.6, Кф6=1.9, Кф4=0.567.

Поскольку все резисторы имеют прямоугольную форму, нет ограничений по площади подложки и точность не высока, выбираем метод свободной маски. По таблице определяем технологические ограничения на масочный метод: Δb=Δl=0.01мм, bтехн=0.1мм, lтехн=0.3мм, аmin=0.3мм, bmin=0.1мм.

Рассчитаем каждый из резисторов.

Расчётную ширину определяем из bрасч≥max(bтехн, bточн,bр),

Δb+Δl/Кф Р

bточн≥------------, bр=(--------)^2.

δ0кф Р0*Кф

За ширину резистора-b принимают ближайшее значение к bрасч, округлённое до целого числа, кратного шагу координатной сетки.

bр1,3,5=0.375мм, bтехн=0.1мм, bточн=0.8мм, значит b1,3,5=0.8мм.

Расчётная длина резистора lрасч=b*Кф. За длину резистора принимают ближайшее к lрасч, кратное шагу координатной сетки значение.

Полная длина напыляемого слоя резистора lполн=l+2*lк. Таким образом lрасч=1.066мм, а lполн=1.466, значит l1,3,5=1.5мм.

Рассчитаем площадь, занимаемую резистором S=lполн*b. S1,3,5=1.2мм^2.

Аналогичным образом рассчитываем размеры резистора R6.

b6=0.7мм, lполн=1.75мм, S=1.225мм^2.

Для резисторов, имеющих Кф<1, сначала определяют длину, а затем ширину. Расчётное значение длины выбирают из условий

Δl+Δb*Кф Р*Кф

lрасч≥max(lтехн,lточн,lр), lточн≥------------, lр=(--------)^1/2.

δ0кф Р0

lточн2=0.736мм, lр2=0.417мм, значит l2=0.75мм.

bрасч=l/Кф, bрасч2=1.25мм, S=0.9375мм^2.

Аналогично рассчитываем R4/

lточн=0.72мм, lр=0.25мм, l4=0.75мм.

b4=1.35мм, S=1.0125мм^2.

Резисторы спроектированы удовлетворительно, т.к.:

1) удельная мощность рассеивания не превышает допустимую

Р01=Р/S≤Р0;

2) погрешность коэффициента формы не превышает допустимую

δ0кф1=Δl/lполн+Δb/b≤δ0кф;

3) суммарная погрешность не превышает допуск

δ0r1=δ0ρ+δ0кф+δ0rt+δ0rст+δ0rк≤δ0r.

3. Выбор подложки.

В качестве материала подложки мы уже выбрали ситалл.

Площадь подложки вычисляют из соотношения

Sr+Sc+Sk+Sн

Sподл=------------------, где

Кs

Кs-коэффициент использования платы (0.4....0.6);

Sr-суммарная площадь, занимаемая резисторами;

Sc-общая площадь, занимаемая конденсаторами;

Sk-общая площадь, занимаемая контактными площадками;

Sн-общая площадь, занимаемая навесными элементами.

Sподл=86.99мм^2.

Выбирем подложку 8×10мм. Толщина-0.5мм.

4. Последовательность технологических операций.

- Напыление материала резистивной плёнки.

- Напыление проводящей плёнки.

- Фотолитография резистивного и проводящего слоёв.

- Нанесение защитного слоя.

- Крепление навесных компонентов.

- Крепление подложки в корпусе.

- Распайка выводов.

- Герметизация корпуса.

Площадки и проводники формируются методом свободной маски.

Защитный слой наносится методом фотолитографии.

5. Выбор корпуса ГИС.

Для ГИС частного применения в основном используется корпусная защита, предусматриваемая техническими условиями на разработку. Выберем корпус, изготавливаемый из пластмассы. Его выводы закрепляются и герметизируются в процессе литья и прессования.

Размеры корпуса (габаритные) 19.5мм×14.5мм, количество выводов–14, из них нам потребуется 10.

6. Оценка надёжности ГИС.

Под надёжностью ИМС понимают свойство микросхем выполнять заданные функции, сохраняя во времени значения установленных эксплуатационных показателей в заданных пределах, соответствующим заданным режимам и условиям использования, хранения и транспортирования.

Расчёт надёжности ГИС на этапе их разработки основан на определении интенсивности отказов-λ(t) и вероятности безотказной работы-Р(t) за требуемый промежуток времени.

1. Рассчитаем λ по формуле:

λi=αi*Ki*λ0i,

где λ0i-зависимость от электрического режима и внешних условий, αi=f(T,Kн)-коэффициент, учитывающий влияние окружающей температуры и электрической нагрузки, Кi=K1-коэффициент, учитывающий воздействие механических нагрузок.

Воздействие влажности и атмосферного давления не учитываем, т.к. микросхема герметично корпусирована.

Для расчётов рекомендуются следующие среднестатистические значения интенсивностей отказов:

- навесные транзисторы λ0т=10^-8 1/ч;

- тонкоплёночные резисторы λ0R=10^-9 1/ч;

- керамические подложки λ0п=5*10^-10 1/ч;

- плёночные проводники и контактные площадки λ0пр=1.1*10^-91/ч;

- паяные соединения λ0соед=3*10^-9 1/ч.

Коэффициенты αi берём из таблиц, приведённых в справочных материалах.

Коэффициенты нагрузки определяются из соотношений:

- транзисторов

КHI=II/IIдоп,

Кнт=max

Кнu=Ui/Uiдоп,

где I-ток коллектора соответствующего транзистора,U-напряжение коллектор-эммитер соответствующего транзистора,Iдоп, Uдоп-допустимые значения токов и напряжений;

- резисторов

КнR=Рi/Рiдоп,

где Рi-рассеиваемая на транзисторе мощность,

Рiдоп-допустимая мощность рассеивания.

Для различных условий экплуатации значения коэффициента в зависимости от нагрузок разные, выберем самолётные-К1=1.65.

После расчётов имеем:

Кнт1=0.0225 αт1=0.4 |

Кнт2=0.0018 αт2=0.4 |

Кнт3=0.045 αт3=0.4 |

Кнт4=0.11 αт4=0.4 |

КнR1=0.23 αR1=0.8 |

КнR2=0.062 αR2=0.7 |

КнR3=0.56 αR3=1.1 |

КнR4=0.37 αR4=0.95 |

КнR5=0.95 αR5=1.5 |

КнR6=1 αR6=1.6 |

λт1234=6.6*10^-9 |

λR1=1.32*10^-9 |

λR2=1.55*10^-9 |

λR3=1.815*10^-9 |

λR4=1.57*10^-9 |

λR5=2.48*10^-9 |

λR6=2.64*10^-9 |

λ0соед=1.09*10^-7 |

λ0пр=4.46*10^-7 |

Величина интенсивности отказов ГИС-λ∑ определяется как сумма всех рассчитанных интенсивностей. Расчётное значение вероятности безотказной работы за время составляет

Р(t)=е^-λ∑t

и равна 0.995 (за 8000 часов).

Список литературы.

- Н. Н. Ушаков "Технология производства ЭВМ". 1991г. Высшая школа.

- Б. П. Цицин "Учебное пособие для выполнения курсового проекта по курсу "Технология производства ЭВМ". 1989г. МАИ.