Синтез цифрового конечного автомата Мили

Министерство науки, высшей школы и технической политики Российской Федерации.

Новосибирский Государственный

Технический Университет.

Расчётно-графическая работа по схемотехнике.

Синтез цифрового конечного автомата Мили.

Вариант №3.

Факультет: АВТ.

Кафедра: АСУ.

Группа: А-513.

Студент: Борзов Андрей Николаевич.

Преподаватель: Машуков Юрий Матвеевич.

Дата: 20 мая 1997 года.

Новосибирск – 1997.

Синтез цифрового конечного автомата Мили.- Построение графа конечного автомата.

- Для заданного графа составить таблицу переходов и таблицу выходов.

- Составляется таблица возбуждения памяти автомата.

- Синтезируется комбинационная схема автомата.

- Составить полную логическую схему автомата на указанном наборе элементов или базисе.

- Составить электрическую схему на выбранном наборе интегральных микросхем.

RS - триггер.

Базис LOGO (ЛОГО).

Вершина графа | a1 | a2 | a3 | a4 | ||||

Сигнал | Zi | Wj | Zi | Wj | Zi | Wj | Zi | Wj |

Дуга из вершины | 1234 | 1234 | 1234 | 1234 | 1234 | 1234 | 1234 | 1234 |

Соответствующие дугам индексы сигналов | 0024 | 0034 | 2014 | 2013 | 0032 | 0042 | 0400 | 0100 |

Z2W2

a1 a2

Z4W4 Z1W1

Z2W3 Z4W3

Z4W1

Z3W4

a3 a4

Z2W2

Таблицы переходов.a(t+1)=δ(a(t); z(t))

Сост. вх. | a1 | a2 | a3 | a4 |

Z1 | - | a3 | - | - |

Z2 | a3 | a1 | a4 | - |

Z3 | - | - | a3 | - |

Z4 | a4 | a4 | - | a2 |

W(t)=λ(a(t); z(t))

Сост. вх. | a1 | a2 | a3 | a4 |

Z1 | - | W1 | - | - |

Z2 | W3 | W2 | W2 | - |

Z3 | - | - | W4 | - |

Z4 | W4 | W3 | - | W1 |

Для этого используем

K=4 (ak)

P=4 (Zi)

S=4 (Wj)

Определяем число элементов памяти:

r ≥ log2K = 2

Число разрядов входной шины:

n ≥ log2P = 2

Число разрядов выходной шины:

m ≥ log2S = 2

3. Кодирование автомата.Внутреннее состояние | Входные шины | Выходные шины | |||

a1= | 00 | Z1= | 00 | W1= | 00 |

a2= | 01 | Z2= | 01 | W2= | 01 |

a3= | 10 | Z3= | 10 | W3= | 10 |

a4= | 11 | Z4= | 11 | W4= | 11 |

Q1Q2 | x1x2 | y1y2 |

Tδ

x1x2Q1Q2 | 00 | 01 | 10 | 11 |

00 | - | 10 | - | - |

01 | 10 | 00 | 11 | - |

10 | - | - | 10 | - |

11 | 11 | 11 | - | 01 |

Tλ

x1x2Q1Q2 | 00 | 01 | 10 | 11 |

00 | - | 00 | - | - |

01 | 10 | 01 | 01 | - |

10 | - | - | 11 | - |

11 | 11 | 10 | - | 00 |

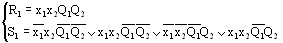

![]() ; (1)

; (1)

![]() . (2)

. (2)

Минимизируем уравнения (1) и (2).

x1x2Q1Q2 | 00 | 01 | 11 | 10 |

00 | X | X | X | |

01 | 1 | X | ||

11 | 1 | 1 | X | |

10 | X | 1 |

x1x2Q1Q2 | 00 | 01 | 11 | 10 |

00 | X | X | X | |

01 | 1 | 1 | ||

11 | 1 | X | X | |

10 | X | 1 |

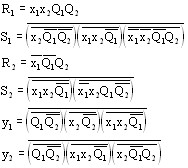

![]() ;

; ![]() .

.

вх. сигн | Q1 | 0 | Q2 | 0 | Q1 | 0 | Q2 | 1 | Q1 | 1 | Q2 | 0 | Q1 | 1 | Q2 | 1 | |||

x1,x2 | R1 | S1 | R2 | S2 | R1 | S1 | R2 | S2 | R1 | S1 | R2 | S2 | R1 | S1 | R2 | S2 | |||

00 | 0 | 1 | 1 | 0 | |||||||||||||||

01 | 0 | 1 | – | 0 | – | 0 | 1 | 0 | 0 | – | 0 | 1 | |||||||

10 | 0 | – | – | 0 | |||||||||||||||

11 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | – | 1 | 0 | 0 | – |

x1x2Q1Q2 | 00 | 01 | 11 | 10 |

00 | ||||

01 | X | |||

11 | 1 | |||

10 |

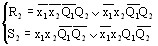

![]()

x1x2Q1Q2 | 00 | 01 | 11 | 10 |

00 | 1 | |||

01 | X | 1 | ||

11 | ||||

10 | X |

![]()

x1x2Q1Q2 | 00 | 01 | 11 | 10 |

00 | 1 | |||

01 | 1 | X | ||

11 | 1 | 1 | ||

10 | X |

![]()

x1x2Q1Q2 | 00 | 01 | 11 | 10 |

00 | ||||

01 | 1 | |||

11 | 1 | X | X | |

10 |

![]()

Логические элементы.

К176ЛЕ5 К176ЛА8 К176ЛА7 К176ЛА9

DD1 – К176ЛЕ5

DD2 – К176ЛА8

DD3 – К176ЛА7

DD4 – К176ЛА9

DD5 – К176ТВ1

Реализуем электрическую схему на базе типовой интегральной серии микросхем К176.