Разработка схемы электронного эквалайзера

МИНИСТЕРСТВО ПУТЕЙ СООБЩЕНИЯ РФ

Московский Государственный Университет Путей Сообщения

Кафедра «РЭС»

Курсовой проект по дисциплине:

«Микропроцессорные информационно-управляющие системы связи»

на тему: «Разработка эквалайзера».

Выполнил студ. гр. АТС-531

Проверил

.

Москва 2004

Содержание

Введение | 3 |

Задание к курсовому проекту | 4 |

Цифровая фильтрация | 5 |

Характеристика FIRF | 6 |

Определение порядка и синтез коэффициентов цифрового фильтра, входящих в состав эквалайзера | 7 |

Общая схема DSP-система | 16 |

Организация интерфейса между устройствами аналогового ввода-вывода, кодеками и DSP-процессорами | 18 |

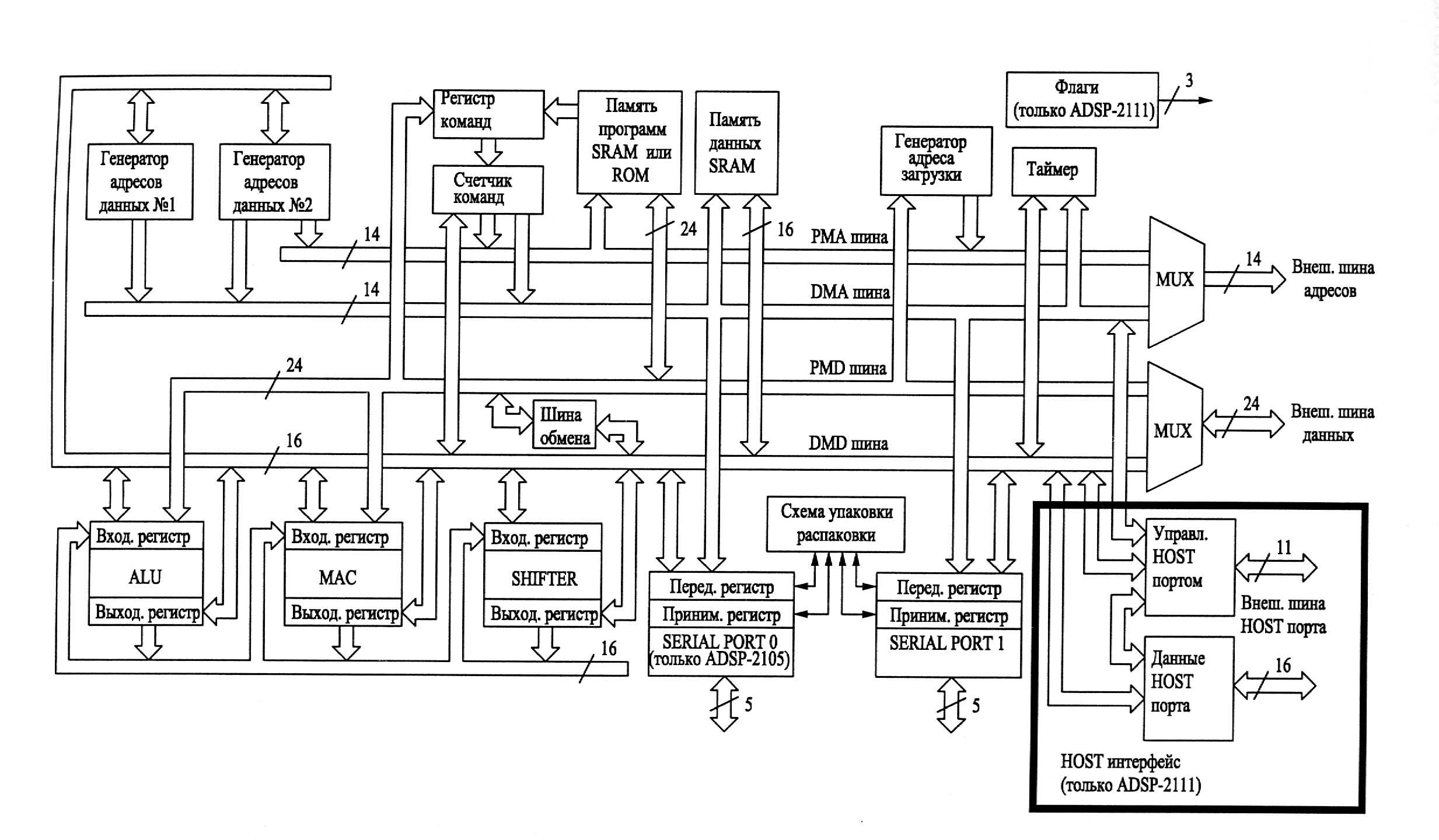

Структурная схема ИС ADSP-2111 | 19 |

| Вывод | 22 |

Список использованной литературы | 23 |

Введение

Цифровой эквалайзер (многополюсный регулятор тембра) – это набор активных фильтров с амплитудами, настраиваемыми на создание формы передаточной функции ряда частотных полос.

Коэффициенты всех фильтров, образующих эквалайзер, хранятся в памяти сигнального процессора и считываются при настройке процессора на пропускание сигнала через соответствующий фильтр.

На одном сигнальном процессоре программно реализуется весь набор цифровых фильтров. Выборки сигнала частично хранятся в кольцевом буфере процессора и постоянно обновляются.

Вычисления проводятся в реальном масштабе времени, поэтому быстродействие процессора должно быть соотнесено с частотой дискретизации обрабатываемого сигнала.

Задание к курсовой работе

В курсовой работе необходимо разработать эквалайзер – устройство, относящееся к цифровой обработке сигналов и применяемое в микропроцессорной технике в системах передачи информации.

В курсовом проекте рекомендуется использовать в качестве базового сигнальный процессор семейства ADSP-21xx фирмы ANALOG DEVICES (США), так как процессоры этой фирмы являются оптимальными по соотношению цена/качество и находят широкое применение в отечественных системах цифровой обработки сигналов.

Границы диапазонов частот фильтра представлены таблице 1:

Таблица 1.

ФНЧ | ПФ1 | ПФ2 | ПФ3 | ПФ4 | ||||

Границы диапазонов частот фильтров, кГц | ||||||||

0,54 | 0,54 | 1 | 1 | 2,9 | 2,9 | 7 | 7 | 11 |

Цифровая фильтрация

Цифровой фильтр – это линеиная импульсная система, обеспечивающая преобразование цифрового сигнала в соответствии с некоторой предопределенной АЧХ или АФЧХ, если важна начальная фаза. Пусть аналоговый непрерывный сигнал – есть функция времени x(t). Тогда дискретный сигнал x(nT) может быть получен путем взятия отсчетов аналогового ситнала в моменты времени 0,T,2T,…,nT. В операторной форме это можно представить следующим образом:

![]()

Известно:

![]()

Умножение на ![]() в комплексной области эквивалентно запаздыванию на один такт во временной области.

в комплексной области эквивалентно запаздыванию на один такт во временной области.

Цифровой фильтр описывается разностным уравнением:

a0٠x(n) + a1٠x(n-1) + … + am٠x(n-m) = b0٠y(n) + b1٠y(n-1) + … + bl٠y(n-l),

или уравнением в форме Z-преобразования:

X(Z)٠(a0 + a1٠Z-1 + …+ am٠Z-m) = Y(Z)٠(b0 + b1٠Z-1 + …+ bl٠Z-l).

Как видно из уравнений, при вычислениях в памяти процессора необходимо сохранять два массива постоянных коэффициентов. Массивы значений входных и выходных сигналов обновляются на каждом такте работы системы. Кроме того, для вычисления значения выходного сигнала y(n) необходимо знать все его предыдущие значения и соответствующие им значения входного сигнала (x должен храниться m тактов после поступления).

Таким образом, при вычислении необходим массив из m членов, который сдвигается на каждом такте. Работа с таким массивом занимает много времени, поэтому реально используют кольцевые буферы цифровых сигнальных процессоров.

Для того, чтобы система обладала заданными свойствами, требуется наити коэффициенты разностных уравненийили передаточную функцию. Передаточная функция для импульсных систем в форме Z-преобразования выглядит следующим образом:

Y(p)/X(p)=H(Z).

Различают два вида фильтрации дискретных сигналов-нерекурсивную и рекурсивную. Деиствительная нерекурсивная фильтрация сигнала x(nT) задается выражением:

y(n) =∑ ak٠x(n-k).

Это уравнение фильтра с конечным импульсным откликом. Под импульсным откликом понимаем импульсную переходную функцию k(t) фильтра, то есть его реакцию на функцию.

Деиствительная рекурсивная фильтрация задается выражением:

y(n) =∑ ak٠x(n-k) + ∑ bk٠y(n-k).

Принципиальное отличие этого выражения от предыдущего в том, что в правой части содержатся значения выходного сигнала. Импульсная переходная функция такой системы теоретически не может быть равной нулю. Поэтому она носит название фильтра с бесконечным импульсным откликом(IIRF). В обоих выражениях через:

- ak и bk обозначены коэффициенты фильтрации;

- N и L-порядки фильтрации;

- y(n) –n-ый отсчет дискретного сигнала,получающегося в результате фильтрации.

Следует отметить, что если допустить N=1, то рекурсивная фильтрация всегда может быть заменена нерекурсивной фильтрацией. В частности, рекурсивная фильтрация с N=1. L=1. эквивалентна нерекурсивной фильтрации с N.

Характеристика уравнения фильтра с конечным импульсным откликом.

Уравнения фильтра с конечным импульсным откликом имеют некоторые конструктивные преимущества по сравнению с уравнениями фильтра бесконечных импульсных откликов.

1. Структурная устоичивость.

Разностное уравнение фильтра с конечным импульсным откликом содержит только правую часть. Это значит, что передаточная функция не содержит знаменателя:

H(Z) = ![]() = a0 + a1٠Z-1 + …+ am٠Z-m.

= a0 + a1٠Z-1 + …+ am٠Z-m.

Характеристическое уравнение не содержит корней. Следовательно, при любых значениях коэффициентов ai система будет устоичива к колебениям.

2. Отсутствие накапливаемой ошибки.

В уравнение не входят значения выходного сигнала, а только входного; следовательно, по истечении времени реакции все последствия неправильного задания начальных условий исчезнут.

3. Нерекурсивный фильтр имеет прототип в области непрерывных сигналов, что важно при решении задач с переходом из цифровой области в аналоговую.

4. Для работы с нерекурсивными фильтрами создано больше компьютерных программ. К тому же они работают лучше.

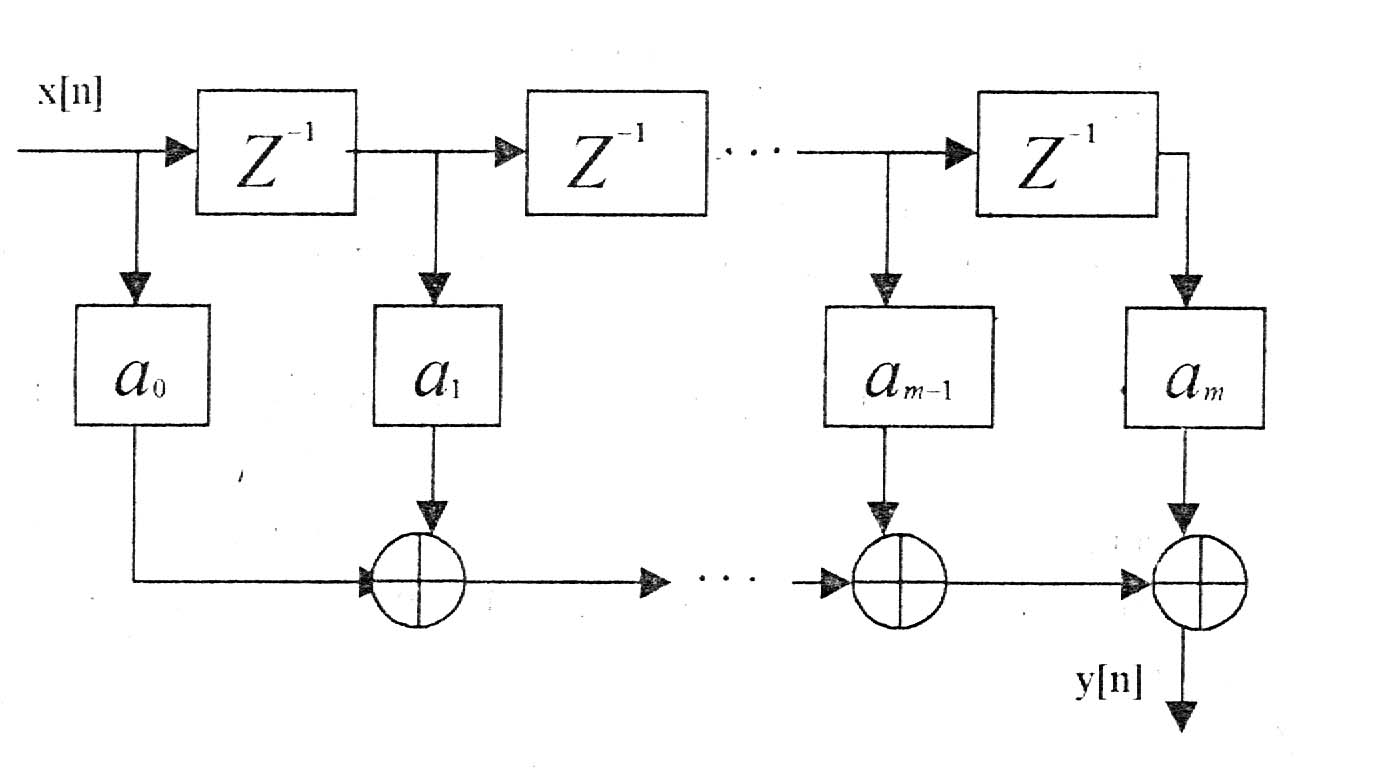

5. Структурная схема фильтра с конечным импульсным откликом представлена на рисунке 1:

Рис.1. Синтез коэффициентов фильтра с конечным импульсным откликом.

6. Недостатком нерекурсивных фильтров является то, что они вносят принципиальное запаздывание. Чтобы получить первое значение выходного сигнала, необходимо ждать m тактов для заполнения массива входных значений. Поэтому нерекурсивная фильтрация используется в приложениях, не критичных к величине задержки.

Общий порядок синтеза коэффициентов фильтра следующий:

1) задаться амплитудо-частотной (АЧХ) или амплитудо-фазо-частотной (АФЧХ) характеристиками фильтра;

2) получить импульсную переходную характеристику фильтра k(t), для чего необходимо взять обратное преобразование Фурье от АЧХ или обратное преобразование Лапласа от АФЧХ;

3) найти коэффициенты фильтра, взяв дискретные значения импульсной переходной функции k(nT).

Определение порядка и синтез коэффициентов

Цифровых фильтров, входящих в состав эквалайзера.

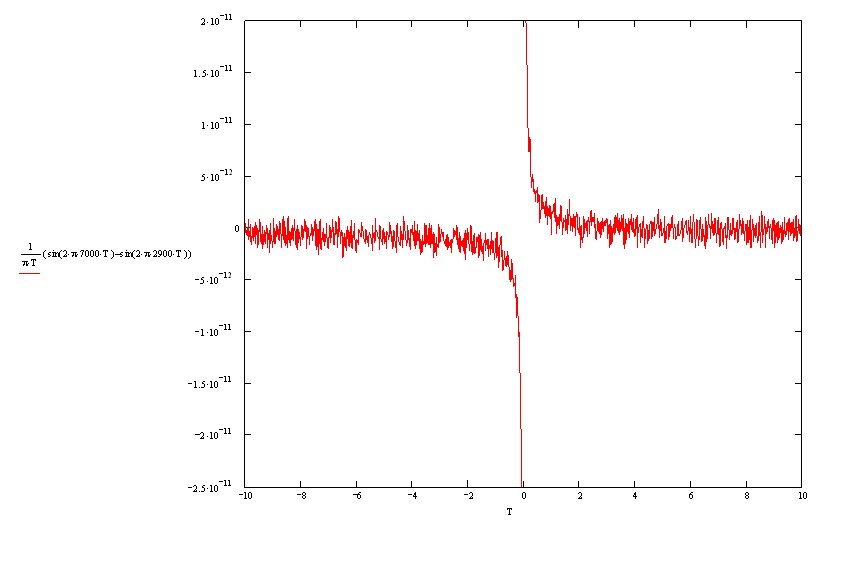

Предположим, что ФЧХ равна 0. Тогда для получения импульсной переходной функции полосового фильтра с полосой пропускания fi-1 ÷ fi достаточно взять обратное преобразование Фурье от АЧХ:

k(t) = 1/2π∫A(ω) ٠ejωtdω = A0/2π∫ejωtdω - A0/2π∫ejωtdω =

=A0/πt(sinωi٠t - sinωi-1٠t), где ωi = 2π fi.

Для исключения погрешности дискретизации выберем частоту дискретизации в два раза выше верхней частоты общей полосы пропускания эквалайзера:

Tд = 2π/ωд = 2π/2ωn = π/ωn = π/(2٠π٠13) = 0,0385 мс.

Продискретизировав импульсную переходную функцию с периодом дискретизации, получим решетчатую функцию k(nTд).

Импульсная переходная функция начинается слева от начала координат. Это невозможно с физической точки зрения, так как нельзя реагировать на событие, которое еще не произошло. Чтобы сместить функцию по оси абсцисс вправо, необходимо внести запаздывание. Однако, если импульсная переходная функция бесконечна, то необходимо внести бесконечное запаздывание, что невозможно. Реально берут 2N+1 отсчетов решетчатой функции, что соответствует запаздыванию на NTд.

В рамках курсового проекта порядок фильтра ограничивается следующей величиной:

N ≥ tдоп/Tд,

где tдоп – время, через которое k(t) ≤ 0,1٠k0,

k0 = k(t)max.

Фильтр нижних частот (ФНЧ).

Частота среза фильтра: ![]() кГц;

кГц;

![]() рад/с;

рад/с;

Частота дискретизации ![]() кГц;

кГц;

Период дискретизации фильтра для определения порядка данного фильтра:

![]() мс.

мс.

Переходная функция ![]() :

:

![]() .

.

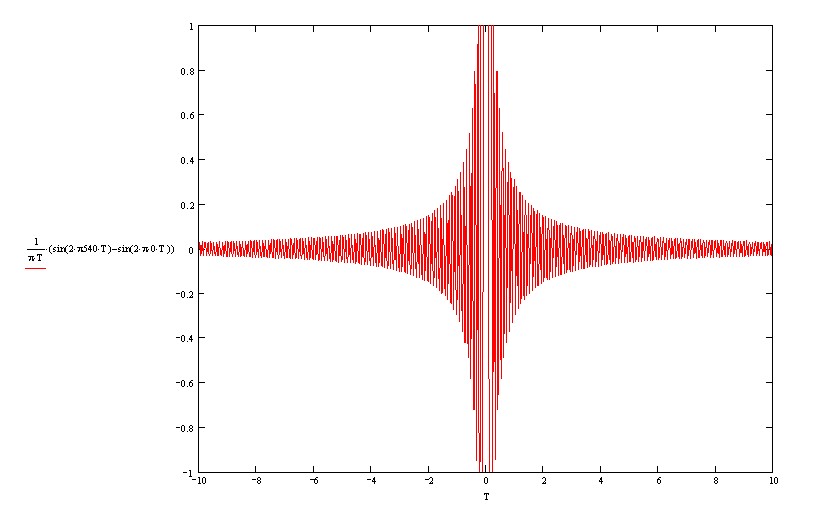

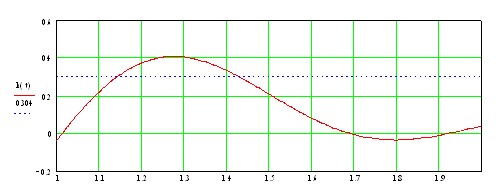

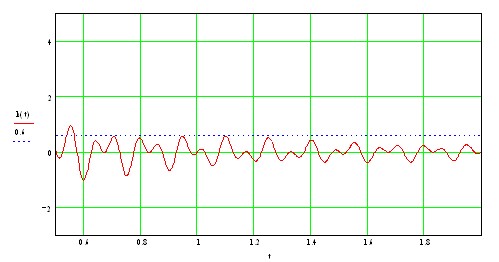

Рис.3. Переходная функция ФНЧ.

Рис.3. Переходная функция ФНЧ.

![]()

![]()

![]()

![]()

Определим коэффициенты фильтра ФНЧ:

Таблица 2.

n a n a n a n a

0 | -0,050849552 | 21 | 0,05213266 | 41 | -0,057902897 | 61 | 0,066693601 |

1 | -0,047381452 | 22 | 0,044603043 | 42 | -0,046254347 | 62 | 0,047455709 |

2 | -0,042531604 | 23 | 0,035644122 | 43 | -0,032920949 | 63 | 0,02589646 |

3 | -0,036405607 | 24 | 0,025465445 | 44 | -0,018209385 | 64 | 0,002473637 |

4 | -0,029146011 | 25 | 0,014314951 | 45 | -0,00247349 | 65 | -0,022284955 |

5 | -0,020929191 | 26 | 0,002473283 | 46 | 0,013893446 | 66 | -0,047790903 |

6 | -0,011961243 | 27 | -0,009752894 | 47 | 0,030467601 | 67 | -0,073406266 |

7 | -0,002473018 | 28 | -0,02203843 | 48 | 0,046804595 | 68 | -0,098456107 |

8 | 0,007285626 | 29 | -0,034047894 | 49 | 0,062450287 | 69 | -0,122242231 |

9 | 0,017052183 | 30 | -0,045444252 | 50 | 0,07695216 | 70 | -0,144057845 |

10 | 0,026558333 | 31 | -0,055897815 | 51 | 0,089871011 | 71 | -0,163202823 |

11 | 0,035537068 | 32 | -0,065095206 | 52 | 0,100792694 | 72 | -0,178999256 |

12 | 0,04372993 | 33 | -0,072748139 | 53 | 0,109339601 | 73 | -0,190806934 |

13 | 0,050894174 | 34 | -0,078601768 | 54 | 0,115181622 | 74 | -0,198038431 |

14 | 0,056809654 | 35 | -0,082442378 | 55 | 0,118046281 | 75 | -0,200173423 |

15 | 0,061285263 | 36 | -0,084104208 | 56 | 0,117727803 | 76 | -0,196771935 |

16 | 0,06416472 | 37 | -0,083475205 | 57 | 0,114094848 | 77 | -0,187486186 |

17 | 0,065331569 | 38 | -0,080501546 | 58 | 0,107096699 | 78 | -0,172070753 |

18 | 0,064713212 | 39 | -0,075190761 | 59 | 0,096767723 | 79 | -0,150390796 |

19 | 0,062283872 | 40 | -0,067613365 | 60 | 0,083229939 | 80 | -0,122428134 |

20 | 0,058066372 |

n a

81 | -0,088285002 |

82 | -0,048185366 |

83 | -0,002473726 |

84 | 0,048388594 |

85 | 0,103829644 |

86 | 0,163175427 |

87 | 0,225660716 |

89 | 0,356611612 |

90 | 0,423214887 |

91 | 0,489266451 |

92 | 0,553768875 |

93 | 0,615731167 |

94 | 0,674187436 |

95 | 0,728215241 |

96 | 0,77695324 |

97 | 0,819617762 |

98 | 0,855517962 |

99 | 0,884069233 |

100 | 0,904804592 |

101 | 0,917383797 |

102 | 0,9216 |

Таким образом, получим 2*N+1=103..

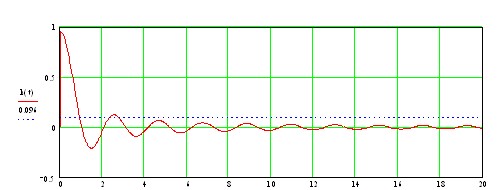

Полосовой фильтр 1. (ПФ1)

Частоты среза фильтра: ![]() кГц,

кГц, ![]() кГц ;

кГц ;

![]() рад/с;

рад/с;

![]() рад/с;

рад/с;

Частота дискретизации fД=13 кГц;

Период дискретизации фильтра для определения порядка данного фильтра:

![]() мс.

мс.

Переходная функция ![]() :

:

![]() .

.

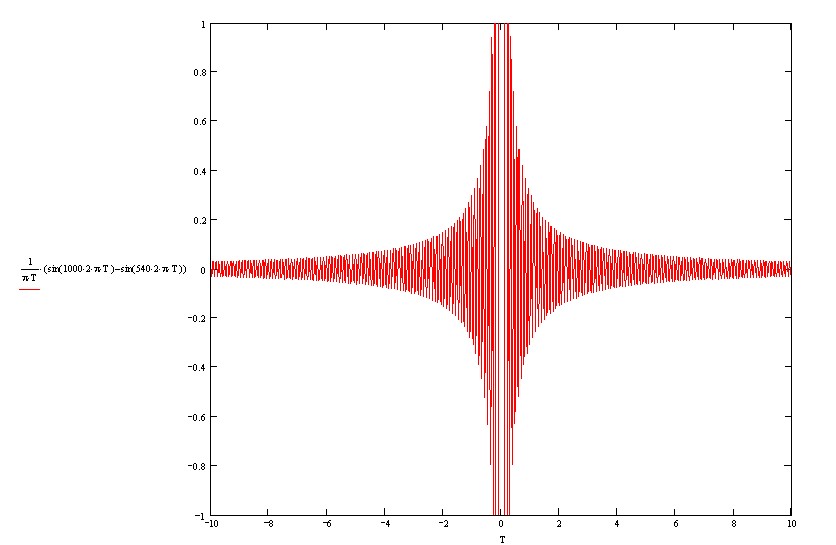

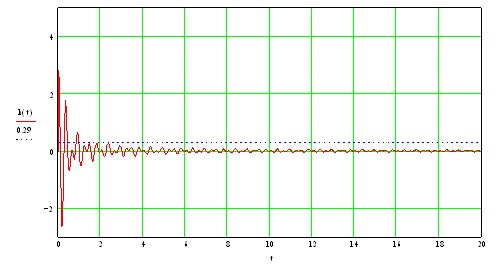

Рис.4. Переходная функция ПФ1.

![]()

![]()

![]()

Определим коэффициенты фильтра ПФ1:

Таблица 3.

n | a | 27 | 0,050566544 |

0 | -0,027392762 | 28 | 0,009754081 |

1 | -0,049172612 | 29 | -0,011037791 |

2 | -0,057498995 | 30 | -0,001629017 |

3 | -0,049981285 | 31 | 0,033889051 |

4 | -0,031300945 | 32 | 0,077854621 |

5 | -0,011253529 | 33 | 0,106118285 |

6 | -0,000340822 | 34 | 0,098772242 |

7 | -0,004862821 | 35 | 0,049903812 |

8 | -0,023768747 | 36 | -0,028191457 |

9 | -0,048803001 | 37 | -0,108781867 |

10 | -0,068018861 | 38 | -0,161509497 |

11 | -0,071175102 | 39 | -0,166035038 |

12 | -0,054593763 | 40 | -0,122644307 |

13 | -0,023199651 | 41 | -0,054716469 |

14 | 0,011335417 | 42 | -0,001027688 |

15 | 0,035666075 | 43 | -9,11331E-05 |

16 | 0,040864762 | 44 | -0,072393216 |

17 | 0,026753627 | 45 | -0,207878004 |

18 | 0,002377281 | 46 | -0,36456585 |

19 | -0,017802566 | 47 | -0,480163419 |

20 | -0,020450558 | 48 | -0,493412799 |

21 | 0,000250373 | 49 | -0,367750032 |

22 | 0,039336231 | 50 | -0,108340337 |

23 | 0,082625786 | 51 | 0,234522697 |

24 | 0,112674731 | 52 | 0,57791205 |

25 | 0,116628962 | 53 | 0,831063217 |

26 | 0,09245668 | 54 | 0,924 |

Таким образом, получим 2*27+1=55.

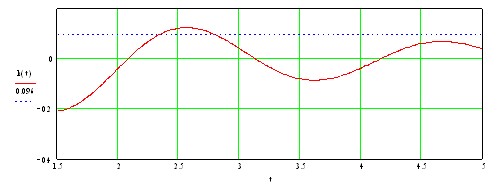

Полосовой фильтр 2. (ПФ2)

Частоты среза фильтра: ![]() кГц,

кГц, ![]() кГц ;

кГц ;

![]() рад/с;

рад/с;

![]() рад/с;

рад/с;

Частота дискретизации fД=18 кГц;

Период дискретизации фильтра для определения порядка данного фильтра:

![]() мс.

мс.

Переходная функция ![]() :

:

![]() .

.

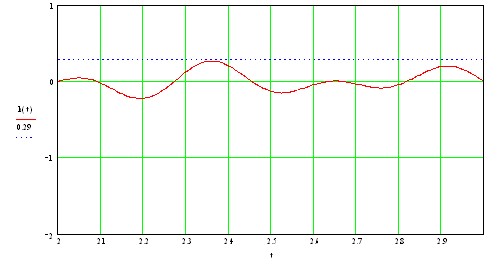

Рис.5. Переходная функция ПФ2.

![]()

![]()

![]()

Определим коэффициенты фильтра ПФ2:

Таблица 4.

n | a | n | a | n | a | n | a |

0 | -0,011403272 | 26 | 0,008564942 | 51 | -0,008846573 | 76 | -0,18082 |

1 | -0,000671233 | 27 | 0,021102423 | 52 | 0,037595032 | 77 | -0,1784 |

2 | -0,002996937 | 28 | 0,004265003 | 53 | 0,080410875 | 78 | 0,095797 |

3 | -0,018770032 | 29 | -0,036469236 | 54 | 0,051282637 | 79 | 0,448421 |

4 | -0,022854085 | 30 | -0,056323545 | 55 | -0,042798877 | 80 | 0,481368 |

5 | 0,001126855 | 31 | -0,024681939 | 56 | -0,112227487 | 81 | 0,024559 |

6 | 0,034325515 | 32 | 0,032843223 | 57 | -0,083934873 | 82 | -0,58945 |

7 | 0,040979404 | 33 | 0,059807045 | 58 | 0,010970719 | 83 | -0,77512 |

8 | 0,011187719 | 34 | 0,033616102 | 59 | 0,072924662 | 84 | -0,27695 |

9 | -0,025443793 | 35 | -0,010193441 | 60 | 0,052722936 | 85 | 0,516062 |

10 | -0,033795035 | 36 | -0,024329191 | 61 | 0,004870193 | 86 | 0,897 |

11 | -0,013271274 | 37 | -0,007485342 | 62 | 0,006592027 | ||

12 | 0,005692888 | 38 | 0,000376818 | 63 | 0,047575263 | ||

13 | 0,002823747 | 39 | -0,022171202 | 64 | 0,039797492 | ||

14 | -0,007074135 | 40 | -0,043667715 | 65 | -0,056146793 | ||

15 | 0,002253171 | 41 | -0,019772772 | 66 | -0,152792284 | ||

16 | 0,028241957 | 42 | 0,041957097 | 67 | -0,123885355 | ||

17 | 0,037692296 | 43 | 0,079697904 | 68 | 0,034673544 | ||

18 | 0,008942625 | 44 | 0,047836289 | 69 | 0,175624872 | ||

19 | -0,035597973 | 45 | -0,025176686 | 70 | 0,159227505 | ||

20 | -0,051085442 | 46 | -0,066753777 | 71 | 0,017255804 | ||

21 | -0,02221679 | 47 | -0,044175408 | 72 | -0,085824627 | ||

22 | 0,01877206 | 48 | 0,001261156 | 73 | -0,058283491 | ||

23 | 0,031228765 | 49 | 0,012420123 | 74 | 0,003729665 | ||

24 | 0,013463011 | 50 | -0,008885547 | 75 | -0,047156433 | ||

25 | -0,000947481 |

Таким образом, получим: 2*N+1=87.

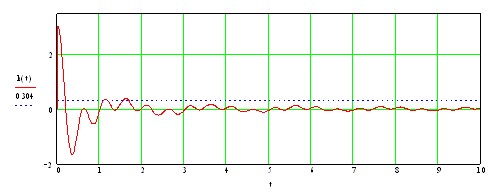

Полосовой фильтр 3. (ПФ3)

Частоты среза фильтра: ![]() кГц,

кГц, ![]() кГц ;

кГц ;

![]() рад/с;

рад/с;

![]() рад/с;

рад/с;

Частота дискретизации fД=18 кГц;

Период дискретизации фильтра для определения порядка данного фильтра:

![]() мс.

мс.

Переходная функция ![]() :

:

![]() .

.

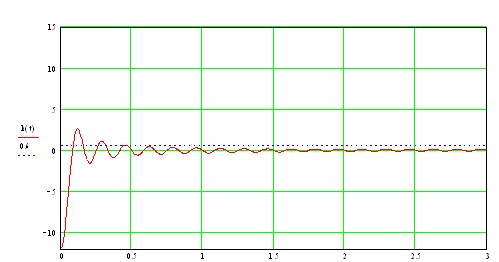

Рис.6. Переходная функция ПФ3.

![]()

![]()

![]()

Определим коэффициенты фильтра ПФ3:

Таблица 5.

n | a | n | a | n | a |

0 | 0,040797115 | 16 | -0,020022291 | 32 | 0,033266 |

1 | 0,001220133 | 17 | 0,055837751 | 33 | 0,260118 |

2 | 0,039978222 | 18 | 0,098343639 | 34 | -0,09252 |

3 | 0,02276506 | 19 | -0,121159876 | 35 | -0,25744 |

4 | -0,105348775 | 20 | -0,099106166 | 36 | 0,086745 |

5 | -0,016132812 | 21 | 0,105674587 | 37 | 0,060059 |

6 | 0,099578035 | 22 | 0,034090375 | 38 | 0,051138 |

7 | 0,000120154 | 23 | 0,00765609 | 39 | 0,204207 |

8 | -0,018054176 | 24 | 0,033408102 | 40 | -0,26949 |

9 | -0,004859298 | 25 | -0,15056655 | 41 | -0,34219 |

10 | -0,082884453 | 26 | -0,049309806 | 42 | 0,383098 |

11 | 0,033032806 | 27 | 0,20912763 | 43 | 0,239879 |

12 | 0,12739375 | 28 | 0,019199721 | 44 | -0,17655 |

13 | -0,050946367 | 29 | -0,114030202 | 45 | 0,0433 |

14 | -0,081052541 | 30 | 0,000617104 | 46 | -0,43205 |

15 | 0,02041495 | 31 | -0,089953059 | 47 | -0,30865 |

48 | 1,286545 | ||||

49 | 0,361651 | ||||

50 | -2,03978 | ||||

51 | -0,1583 | ||||

52 | 2,34 |

Таким образом, получим: 2*N+1=53

Полосовой фильтр №4 (ПФ4)

Частоты среза фильтра: ![]() кГц,

кГц, ![]() кГц ;

кГц ;

![]() рад/с;

рад/с;

![]() рад/с;

рад/с;

Частота дискретизации fД=18 кГц;

Период дискретизации фильтра для определения порядка данного фильтра:

![]() мс.

мс.

Переходная функция ![]() :

:

![]()

Рис.7. Переходная функция ПФ4.

![]()

![]()

![]()

Определим коэффициенты фильтра ПФ4:

Таблица 6.

n | a | n | a |

0 | -0,039924801 | 13 | -0,14859 |

1 | -0,036859051 | 14 | -0,03612 |

2 | -0,030099957 | 15 | 0,339846 |

3 | 0,181767777 | 16 | -0,44409 |

4 | -0,262616392 | 17 | 0,188865 |

5 | 0,179398893 | 18 | 0,21898 |

6 | -0,00735706 | 19 | -0,34919 |

7 | -0,074570718 | 20 | -0,03768 |

8 | -0,033569017 | 21 | 0,674093 |

9 | 0,236141895 | 22 | -0,90173 |

10 | -0,323321834 | 23 | 0,190798 |

11 | 0,185039538 | 24 | 1,350195 |

12 | 0,056604813 | 25 | -2,93165 |

26 | 1,8 |

Таким образом, получим: 2*N+1=27

Результаты определения порядка фильтров удобно представить в следующем виде:

Таблица 7.

Фильтр | Полоса пропускания | N Tд, с | N | Максимальная точка АЧХ |

ФНЧ1 | 0-0,54 | 0,0042 | 93 | 4,2 |

ПФ1 | 0,54-1 | 0,0043 | 95 | 4,3 |

ПФ2 | 1-2,9 | 0,0162 | 36 | 1,6 |

ПФ3 | 2,9-7 | 0,0009 | 20 | 0,88 |

ПФ4 | 7-11 | 0,0006 | 13 | 0,56 |

После ограничения функции и внесения запаздывания можно произвести вычисление коэффициентов фильтра:

a0=k(0)=a2N;

a1=k(Tд)=a2N-1;

a2=k(2*Tд)=a2N-2;

…

aN=k(N*Tд).

Получив массив коэффициентов, можно записать АФЧХ фильтра с конечным импульсным откликом.

H(Z)=a0+a1*Z^-1+…+a2N+1*Z^-(2N+1), Z=e^jwt

H(jw)=a0+a1*e^-jwt+…+a2N+1*e^-(2N+1)*jwt=a0+a1*Cos(w*Tд)+…+a2N+1*Cos(2N+1)*w*Tд-j*(a1*SinwTд+…+a2N+1*Sin(2N+1)wTд)

Запишем это выражение в более удобной для программирования форме:

H(jw)=Re(w)+jJm(w),

Тогда АЧХ фильтра

/H(jw)/= Re^2(w)+Jm^2(w)

Рис.8. Общая схема DSP-системы

Сигнал, поступающий на аналоговый вход системы предварительно ограничивается по частоте с помощью противопомехового фильтра нижних частот. Затем он передается на АЦП. В выделенный момент дискретизации конвертер прерывает работу процессора и формирует соответствующую выборку.

В DSP входные данные обрабатываются по программному алгоритму. Когда процессор заканчивает необходимые вычисления, он посылает результат в ЦАП. ЦАП конвертирует выход DSP в желаемую аналоговую форму. Выход конвертора сглаживается восстанавливающим фильтром нижних частот.

Произвольный главный машинный интерфейс служит для связи DSP с внешними системами, передающими и принимающими данные и сигналы управления.

Организация интерфейса между устройствами аналогового

ввода-вывода, кодеками и DSP-процессорами.

Так как большинство приложений цифровой обработки сигналов требует наличия одновременно АЦП и ЦАП, то широкое развитие получили универсальные устройства, интегрирующие функции кодека и портов ввода-вывода на одном кристалле и обеспечивающие простое подключение к стандартным DSP-процессорам. Эти устройства называют аналоговыми оконечными устройствами (далее по тексту-AFE-Analog Front End ) .

Функциональная схема микросхемы AD73322 показана на рис.3. Данный прибор представляет собой двойной AFE с двумя 16-разрядными АЦП и двумя 16-разрядными ЦАП с возможностью работы с частотой дискретизации 64 кГц. ИС AD73322 разработана для универсального применения, включая обработку речи и телефонию с использованием сигнал/шум на уровне 77дБ в пределах голосовой полосы частот.

Каналы АЦП и ЦАП имеют программируемые коэффициенты усиления по входу и выходу с диапазонами до 38дБ и 21 дБ соответственно. Встроенный источник опорного напряжения величиной +2ю7-5.5 В. Его потребляемая мощность при напряжении питания +3 В составляет 73 мВт.

Рис. 9. Функциональная схема микросхемы ADSP-2189.

Системный интерфейс DSP

Системный интерфейс представляет собой, набор программный и аппаратных возможностей управления DSP, сигналы управления включают в себя:

- Reset – сигнал сброса,

- Синхроимпульсы,

- Входы флагов,

- Сигналы запроса прерывания

Reset – останавливает выполнение инструкций и осуществляет аппаратный сброс. После сброса значение всех регистров, ВУ и генератора адреса не определенно.

Синхроимпульсы

Процессор использует ТТЛ совместимые импульсы подаваемые на вход CLKIN, или кварцевый резонатор включается между входами CLKIN и XTAL.

Программная загрузка процессора может инициализироваться не только сигналом RESET, но и программным путем. Процессор содержит управляющий регистр и при установке в нем бита BFORCE и 1 инициализируется программная загрузка. Во время программной загрузки все прерывания маскируются.

DSP имеет 1 или несколько входов для внешних прерываний IRQ1 и IRQ0, сюда подключаются сигналы запроса прерываний, каждый из который имеет свой уровень приоритета.

FI – входной флаг, может использоваться в условных командах перехода.

FO – может использоваться для разных целей как выходной управляющий сигнал. Сигнал FO не затрагивается аппаратным сбросом. Все остальные флаги устанавливаются в 1, при аппаратном сбросе.

ADDR – 14 разрядная шина адреса.

DATA – 24 разрядная шина данных.

RW/WR – управление направлением передачи данных (чтение из внешней памяти или запись)

Сигналы BMS, PMS, DMS позволяют выбирать одно из 3-х адресных пространств внешней памяти доступной процессору.

Процессор имеет интерфейс с внешней памятью 3-х видов:

1. Загрузочная память, то откуда производится начальная загрузка программы в процессор. Организованна в виде страниц, делится на 3-х байтные слова ( 24 разряда). Каждая страница имеет свой загрузочный адрес, в котором указан номер станицы, ее длина, и порядок считывания слов из страницы.

2. Память программ. Процессор адресует до 16 Кбайт 24-х разрядных слов памяти программ, из которых 2 Кбайта на кристалле Процессор записывает 14 разрядный. Адрес инструкции на шину PMA, инструкция или данные передаются в ВУ по 24 разрядной шине PMD. Если одновременно производится обращение к внешней памяти данных и внешней памяти программ, то сначала считывается информация из памяти программ. Выбор памяти программ осуществляется сигналом PMS, а направление передачи управляющим сигналом RW/WR. Внешняя память программ может отсутствовать.

3. Память данных. Процессор адресует 16 Кбайт 16 разрядных слов памяти данных, память данных на кристалле имеет объем 1 Кбайт. Данные переносятся по старшим 16 битам 24 разрядной шины данных. вся память данных разделена на 5 областей (внешняя), каждая из этих областей имеет свое число циклов ожидания, устанавливается программным путем. Благодаря этому различные области адресного пространства могут использоваться устройствами имеющими разное быстродействие. Используя запрос шины BR и сигнала прерывания шины BG, процессор может отдавать управление шиной внешнему устройству (HOST интерфейсу). Вход BR является асинхронным. Внешние устройства запрашивают шину установкой сигнала BR. Когда этот сигнал распознан, процессор отвечает установкой сигнала BG в следующем цикле, процессор останавливает свою работу если необходимо и переводит шины адреса и данных, а также сигналы RD/WR, BMS, PMS, DMS в 3-е состояние. После этого управление шиной передается внешнему устройству. Внешнее устройство возвращает управление шиной сбросом сигнала BR, процессор отвечает сбросом сигнала BG. После этого работа процессора возобновляется с того момента где она была приостановлена.

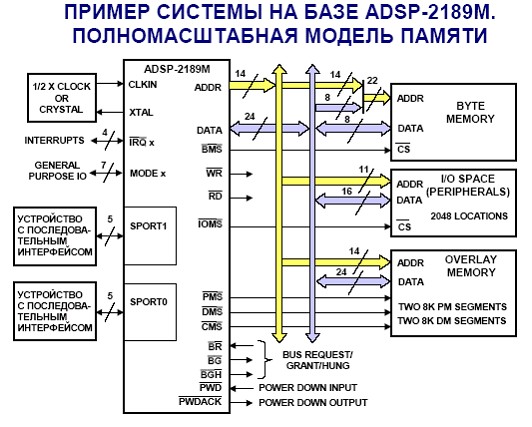

На рис. 10 показана система на базе процессора ADSP-2189M, использующая полномасштабную модель памяти. Она включает два устройства, работающие через последовательные интерфейсы, 8-разрядную EPROM, внешнюю оверлейную память программ и данных. Возможность программной генерации циклов ожидания позволяет легко подключать быстрый процессор к более медленным периферийным устройствам. Процессор ADSP-2189M также поддерживает четыре внешних прерывания, семь универсальных сигналов ввода-вывода и два последовательных порта. Один из последовательных портов может быть сконфигурирован как источник двух дополнительных сигналов прерывания, один универсальный вход и один универсальный сигнал вывода, что даст в сумме шесть внешних сигналов прерывания, девять каналов ввода-вывода общего назначения при сохранении одного полнофункционального последовательного порта. Процессор ADSP-2189M может также работать в режиме доступа к хост-памяти (host memory mode), который позволяет организовать доступ по всей ширине внешней шины данных, но ограничивает адресацию одним адресным битом. Дополнительные периферийные устройства могут быть подключены в режиме host memory mode при использованием внешних аппаратных средств для генерации и фиксации дополнительных адресных сигналов.

Рис.10.

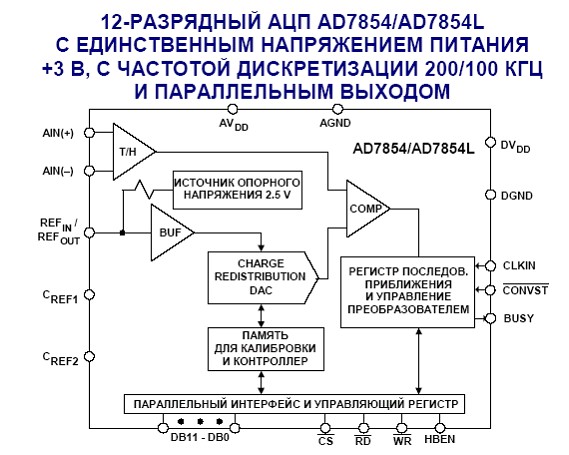

Описание АЦП

В связи с быстрым развитием технологии смешанной аналогово-цифровой обработки сигналов устройства на базе DSP с высокой степенью интеграции, появляющиеся на рынке в настоящее время (например ADSP-21ESP202), имеют помимо DSP-ядра интегрированные АЦП/ЦАП, что снимает проблему организации интерфейса между отдельными компонентами. Дискретные АЦП и ЦАП теперь оснащаются интерфейсами, специально предназначенными для связи с DSP, и тем самым минимизируют или устраняют необходимость внешней поддержки интерфейса или применения интерфейсной логики. Высокопроизводительные сигма-дельта-АЦП и ЦАП в настоящее время выпускаются в одном корпусе (такое комбинированные решение называется КОДЕК или КОдер/ДЕКодер), например, AD73311 и AD73322. Данные устройства также разработаны с учетом минимальных требований к интерфейсной логике при работе с наиболее распространенными DSP-процессорами. В настоящей главе рассматриваются проблемы, связанные с передачей и синхронизацией данных при организации различных интерфейсов.

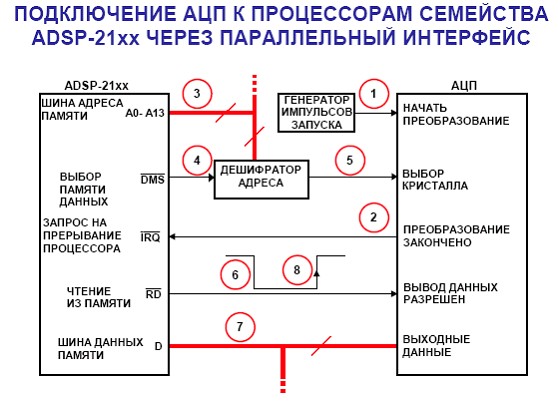

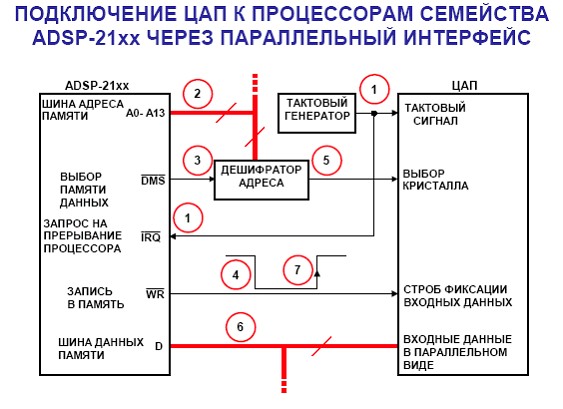

ОРГАНИЗАЦИЯ ПАРАЛЛЕЛЬНОГО ИНТЕРФЕЙСА С DSP-ПРОЦЕССОРАМИ: ЧТЕНИЕ ДАННЫХ ИЗ АЦП, ПОДКЛЮЧЕННОГО С ОТОБРАЖЕНИЕМ В АДРЕСНОЕ ПРОСТРАНСТВО ПАМЯТИ

Подключение АЦП или ЦАП через быстрый параллельный интерфейс к DSP-процессору требует понимания специфики процессов чтения данных DSP-процессором из периферийных устройств (АЦП), а также записи данных процессором в периферийные устройства (ЦАП) при подключении данных устройств в адресное пространство памяти. Вначале мы рассмотрим некоторые основные требования к временным параметрам сигналов, используемых для чтения и записи данных. Необходимо отметить, что принципы, представленные здесь на примере доступа к АЦП и ЦАП, применимы также при чтении и записи в/из внешней памяти.

Блок-схема типичного параллельного интерфейса DSP-процессора с внешним АЦП показана на рис 11. Эта диаграмма сильно упрощена и показывает только сигналы, используемые для чтения данных из внешнего устройства, подключенного в адресное пространство памяти. Использование отдельного задающего генератора для АЦП является предпочтительным, поскольку сигнал внутреннего генератора DSP-процессора может иметь высокий уровень помех и фазовый шум (jitter), который в процессе аналого-цифрового преобразования приведет к увеличению уровня шумов АЦП.

Тактовый импульс задающего генератора на входе "старт преобразования" (convert start) АЦП инициирует процесс преобразования входных данных (шаг N 1). По переднему фронту этого импульса внутренняя схема выборки-хранения АЦП переключается из режима выборки в режим хранения и таким образом начинается процесс преобразования. После выполнения преобразования на выходе АЦП выставляется строб преобразование выполнено (шаг N 2). Когда этот сигнал поступает на вход запроса прерывания DSP-процессора (IRQ), начинается процесс чтения данных из АЦП. Далее процессор выставляет на шине адрес периферийного устройства, инициировавшего запрос на прерывание (шаг N 3). В то же самое время процессор переводит в активное состояние сигнал доступа к памяти (DMS) (шаг N 4). Две внутренние шины адреса в процессоре ADSP-21XX (шина адреса памяти программ и шина адреса памяти данных) совместно используют внешнюю шину адреса, а две внутренние шины данных (шина данных памяти программ и шина данных памяти данных) совместно используют одну внешнюю шину данных. Сигналы выбора памяти начальной загрузки (BMS), выбора памяти данных (DMS), выбора памяти программ (PMS) и выбора памяти устройств ввода-вывода (IOMS) указывают, для какой памяти в данный момент используются внешние шины. Эти сигналы обычно используются для разрешения внешней дешифрации адреса, как показано на рис. 11. Выходной сигнал дешифратора адреса подается на вход chip select выбора периферийного устройства (шаг N 5).

Сигнал чтения памяти (memory read, RD) выставляется через промежуток времени tASR после активации сигнала DMS (шаг N 6). Чтобы полностью использовать преимущество высокой скорости DSP-процессора, сумма времени задержки дешифрации адреса и времени включения периферийного устройства после подачи сигнала выбора (chip select) не должна превышать время tASR. Сигнал чтения памяти (memory read, RD) остается активным (низкий логический уровень) в течение времени tRP. Этот сигнал используется для перевода в активное состояние параллельного выхода данных периферийного устройства (шаг N 7). Сигнал RD обычно подключается к соответствующему выводу периферийного устройства, называемому сигналом разрешения выхода или чтения (output enable или read). Восходящий (задний) фронт сигнала RD используется для ввода данных с шины в DSP-процессор (шаг N 8). После появления восходящего (заднего) фронта сигнала RD данные на шине должны удерживаться периферийным устройством в течение времени tRDH, называемого временем удержания данных. Для большинства процессоров семейства ADSP-21XX это время равно нулю.

Основные требования к временным параметрам периферийного устройства показаны на рис. 11. Все значения даны для процессора ADSP-2189M, работающего на тактовой частоте 75 МГц.

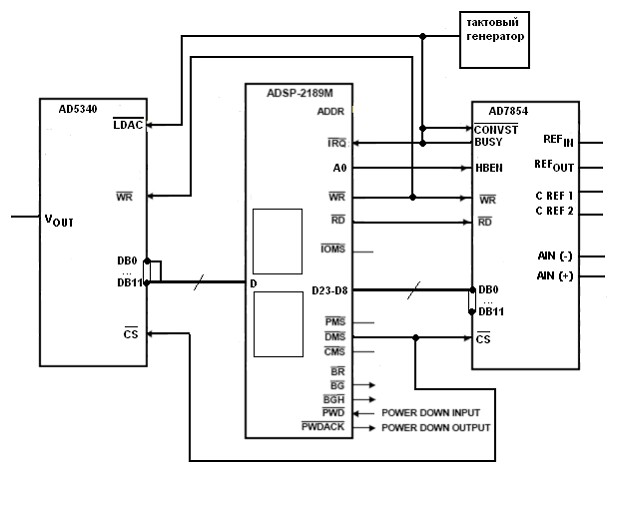

Рис 11. Подключение АЦП.

Процессор ADSP-2189M способен эффективно взаимодействовать с медленными периферийными устройствами при помощи имеющихся средств программирования длительности состояния ожидания. Имеется три специальных регистра для управления процессом ожидания: для памяти начальной загрузки, для памяти программ и для памяти данных и пространства ввода-вывода. Программист может задать от 0 до 15 тактов ожидания для каждого параллельного интерфейса памяти. Каждый такт ожидания увеличивает время доступа к внешней памяти на величину, равную по длительности одному такту генератора тактовых импульсов процессора (13.3 нс для процессора ADSP-2189M, работающего на тактовой частоте 75 МГц). В рассматриваемом примере сигналы адрес памяти данных, DMS и RD удерживаются неизменными в течение дополнительного времени, определяемого продолжительностью тактов ожидания. Микросхемы AD7854/AD7854L – это 12-разрядные АЦП, работающие с частотой отсчетов 100 или 200 кГц, которые имеют параллельный интерфейс. Эти АЦП работают от однополярного источника питания с напряжением от +3 В до +5.5 В и потребляют порядка 5.5 мВт (AD7854L при питании +3 В). Автоматическое переключение микросхемы в энергосберегающий режим после выполнения преобразования снижает потребляемую мощность до 650 мкВт. Функциональная схема AD7854/AD7854L показана на рис. 7.6. ИС AD7854/AD7854L реализует технологию преобразования методом последовательного приближения с применением ЦАП с перераспределением зарядов (ЦАП на переключаемых конденсаторах). Наличие режима калибровки позволяет избавиться от погрешности смещения и погрешности коэффициента усиления. Ключевые временные характеристики параллельного интерфейса между AD7854/AD7854L и ADSP-2189M показаны на рис. 12. Характеристики процессора ADSP-2189M приведены для тактовой частоты равной 75 МГц. Исследование временных соотношений, приведенных на рис 7.7, показывает, что для синхронизации работы двух устройств необходимо введение пяти тактов ожидания для процессора ADSP-2189M. Это увеличивает tRDD до 68.15 нс, что превышает минимальное время доступа к АЦП AD7854/AD7854L (t8 = 50 нс минимум). Длительность импульса чтения - tRP по той же причине увеличивается до 70.15 нс, что позволяет удовлетворить требование к длительности строба чтения (t7 = 70 нс минимум). Если периферийное устройство, включенное в адресное пространство памяти, не обладает чрезвычайно малым временем доступа, то использование режима ожидания совершенно необходимо для организации интерфейса с этим устройством, будь то АЦП, ЦАП или внешняя память.

Рис.12.

Схема интерфейса между двумя устройствами (АЦП и DSP) показана на рис. 13. В качестве сигнала окончания преобразования от AD7854/AD7854L используется сигнал BUSY. Нужно заметить, что показанная конфигурация позволяет DSP-процессору записывать данные в регистр управления параллельным интерфейсом AD7854/AD7854L. Это необходимо для установки различных опций в AD7854/AD7854L и выполнения процесса калибровки. Однако в обычном режиме чтение данных из AD7854/AD7854L осуществляется в соответствии с приведенным выше описанием. Запись в периферийные устройства, включенные в адресное пространство памяти, рассматривается в последующих разделах этой главы.

Параллельные интерфейсы между другими DSP-процессорами и внешними периферийными устройствами могут быть построены подобным способом, однако всякий раз необходимо тщательно изучить временные параметры всех соответствующих сигналов для каждого устройства. Техническая документация большинства АЦП содержит достаточную информацию для организации интерфейса с DSP-процессорами.

Рис.13.

Описание ЦАП

ОРГАНИЗАЦИЯ ПАРАЛЛЕЛЬНОГО ИНТЕРФЕЙСА С DSP-ПРОЦЕССОРАМИ: ЗАПИСЬ ДАННЫХ В ЦАП, ПОДКЛЮЧЕННЫЙ С ОТОБРАЖЕНИЕМ В АДРЕСНОЕ ПРОСТРАНСТВО ПАМЯТИ.

Схема стандартного интерфейса между DSP-процессором и параллельным периферийным устройством (например ЦАП) показана на рис. 14.

В большинстве приложений реального времени ЦАП функционирует непрерывно с постоянной тактовой частотой. Большинство ЦАП, используемых для этих приложений, осуществляет двойную буферизацию данных. Имеется входной регистр для фиксации данных, поступающих через асинхронный интерфейс с DSP-процессором, и далее регистр (называемый регистром хранения ЦАП), который управляет токовыми ключами ЦАП. Регистр хранения ЦАП синхронизируется внешним стабильным генератором, задающим частоту дискретизации. Кроме тактирования регистра хранения ЦАП, данный сигнал используется также для генерации сигнала прерывания DSP-процессора, который указывает на готовность ЦАП к приему новых входных данных.

Рис.14.

Таким образом, процесс записи инициируется периферийным устройством посредством установления сигнала запроса прерывания DSP-процессора, указывающего, что периферийное устройство готово к приему новых данных (шаг N 1). Далее DSP-процессор выставляет адрес периферийного устройства на адресной шине (шаг N 2) и переводит в активное состояние сигнал выбора памяти DMS (шаг N 3). Это приводит к тому, что дешифратор адреса выдает сигнал выбора (chip select) на периферийное устройство (шаг N 5). После спадающего (переднего) фронта сигнала DMS через промежуток времени tASW процессор переводит в активное нулевое состояние сигнал записи WR (шаг N 4). Длительность импульса WR составляет tWP нс. Данные помещаются на шину данных (D) и удерживаются в течение времени tDW, до перехода сигнала WR в неактивное единичное состояние (шаг N 6). Восходящий (задний) фронт сигнала WR используется для фиксации присутствующих на шине данных (D) во внешнюю параллельную память (шаг N 7). Данные на шине остаются достоверными еще в течение времени tDH после прохождения положительного фронта сигнала WR.

Основные требования по временным параметрам при записи данных в периферийное устройство показаны на рис. 14. Главным параметром здесь является длительность строба записи tWP. Для всех периферийных устройств, кроме самых быстрых, придется использовать циклы ожидания, т.к. этим устройствам нужно больше времени для доступа к данным.

Микросхема AD5340 – это 12-ти разрядный ЦАП, работающий на частоте дискретизации 100 кГц, имеющий параллельный цифровой интерфейс. Данный АЦП питается от однополярного источника питания напряжением +2.5-5.5 В и рассеивает мощность 345 мкВт (при напряжении питания 3 В). В энергосберегающем режиме потребляемая мощность прибора снижается до 0.24 мкВт. ЦАП AD5340 имеет в своем составе выходной буферный усилитель, который способен формировать выходной сигнал в диапазоне значений от нуля до напряжения питания. В ИС AD5340 можно задействовать или отключить встроенный буфер для источника опорного напряжения. В устройстве имеется встроенная схема формирования сигнала сброса при включении питания, гарантирующая нулевое значение сигнала на выходе ЦАП до тех пор, пока в ЦАП не будут записаны корректные данные. Структурная схема ЦАП показана на рис. 15. На входе прибора осуществляется двойная буферизация данных. Спецификация временных параметров цикла записи для ADSP-2189M дается для тактовой частоты 75 МГц.

Рис.15.

Исследование временных характеристик, изображенных на рис. 7.14, показывает, что для обеспечения совместимости по синхронизации между устройствами потребуется программирование двух циклов ожидания в процессоре ADSP-2189M. Это позволяет увеличить длительность строба записи (WR) до 30.25 нс, что превышает минимально необходимую длительность строба записи в ЦАП AD5340 (20 нс). Минимальное время установления данных в микросхеме AD5340, равное 5 нс, также перекрывается при использовании двух циклов ожидания. Схема интерфейса между двумя устройствами показана на рис. 16.

Параллельные интерфейсы с другими DSP-процессорами могут быть организованы подобным образом, для чего необходимо подробное изучение временных спецификаций всех соответствующих сигналов каждого из взаимодействующих устройств.

Рис.16.

Рис. 17. Принципиальная схема DSP системы.

Алгоритм работы устройства ADSP-21XX

{М=2NФНЧ+1+2NПФ1+1+2NПФ2+

+1+2NПФ3+1+2NПФ4+1}

{ai, xi – массив, i=1,2..М}

Программа и графики АЧХ фильтров

program k(t);

uses crt,graph;

label 1,2,3;

const f1=1000;

const f2=520;

const fd=20000;

var A,Re,Mn,Td,w1,w2,w,wt,wtp:real;

n,x,y:integer;

Road:STRING;

f:text;

kt:array(0..105) of real;

begin

clrscr;

writeln ('File name?');

readln (road);

assign (f, Road);

rewrite(f);

writeln(f,' w',' ',' A');

w1:=2*pi*f1;

w2:=2*pi*f2;

Td:=1/fd;

n:=0;

w:=0;

x:=detect;

InitGraph(x,y,'c:\tp7\tp7\bgi');

line(0,479,640,479);

line(0,0,0,479);

repeat

wt:=2*pi*w/20000;

re:=0;

mn:=0;

n:=0;

repeat

if n=0 then goto 1 else goto 2;

2:kt(n):=(sin(w1*n*Td)-sin(w2*n*Td))/(pi*n*Td);

goto 3;

1:kt(n):=(w1-w2)/pi;

3:re:=re+kt(n)*cos(wt*n);

mn:=mn+kt(n)*sin(wt*n);

if n=0 then mn:=0;

n:=n+1;

until n>81;

A:=sqrt(sqr(re)+sqr(mn));

writeln (f,' ',w:5:2,' ',A:5:4);

x:=trunc(w/46.88);

putpixel(x,trunc(-A/41.67+480),7);

if w=620 then begin

y:=trunc(-A/41.67+480);

repeat

line(trunc(w/46.88),y,trunc(w/46.88),y+5);

y:=y+20;

until y>479;

end;

if w=1000 then begin

y:=trunc(-A/41.67+480);

repeat

line(trunc(w/46.88),y,trunc(w/46.88),y+5);

y:=y+20;

until y>479;

end;

w:=w+1;

until w>=20000;

close(f);

repeat until keypressed;

end.

Вывод.В курсовой работе был успешно разработан эквалайзер, применяемый в микропроцессорной технике в системах передачи информации.

В качестве базового был использован в качестве сигнальный процессор семейства ADSP-21xx фирмы ANALOG DEVICES. Процессоры этой фирмы являются оптимальными по соотношению цены к качеству и нашли широкое применение в современных системах цифровой обработки сигналов.

Литература1.Методические указания и задания на курсовой проект « Разработка эквалайзера »

2. Курс лекций по дисциплине « МИУСС » -